鈼?/div>

Peripheral Device Controller

鈥?26-bit address bus

鈥?32-bit data bus with variable width support of 8-,16-, or 32-bits

鈥?8-bit boot ROM support

鈥?6 banks available, up to 64MB per bank

鈥?Supports Flash ROM, PROM, SRAM, dual-port memory, and

peripheral devices

鈥?Supports external wait-state generation, Intel or Motorola style

鈥?Write protect capability

鈥?Direct control of optional external data transceivers

鈼?/div>

System Integrity

鈥?Programmable system watchdog timer resets system on time-

out

鈥?Programmable bus transaction times memory and peripheral

transactions and generates a warm reset on time-out

鈼?/div>

DMA

鈥?16 DMA channels

鈥?Services on-chip and external peripherals

鈥?Supports memory-to-memory, memory-to-I/O, and I/O-to-I/O

transfers

鈥?Supports flexible descriptor based operation and chaining via

linked lists of records (scatter / gather capability)

鈥?Supports unaligned transfers

鈥?Supports burst transfers

鈼?/div>

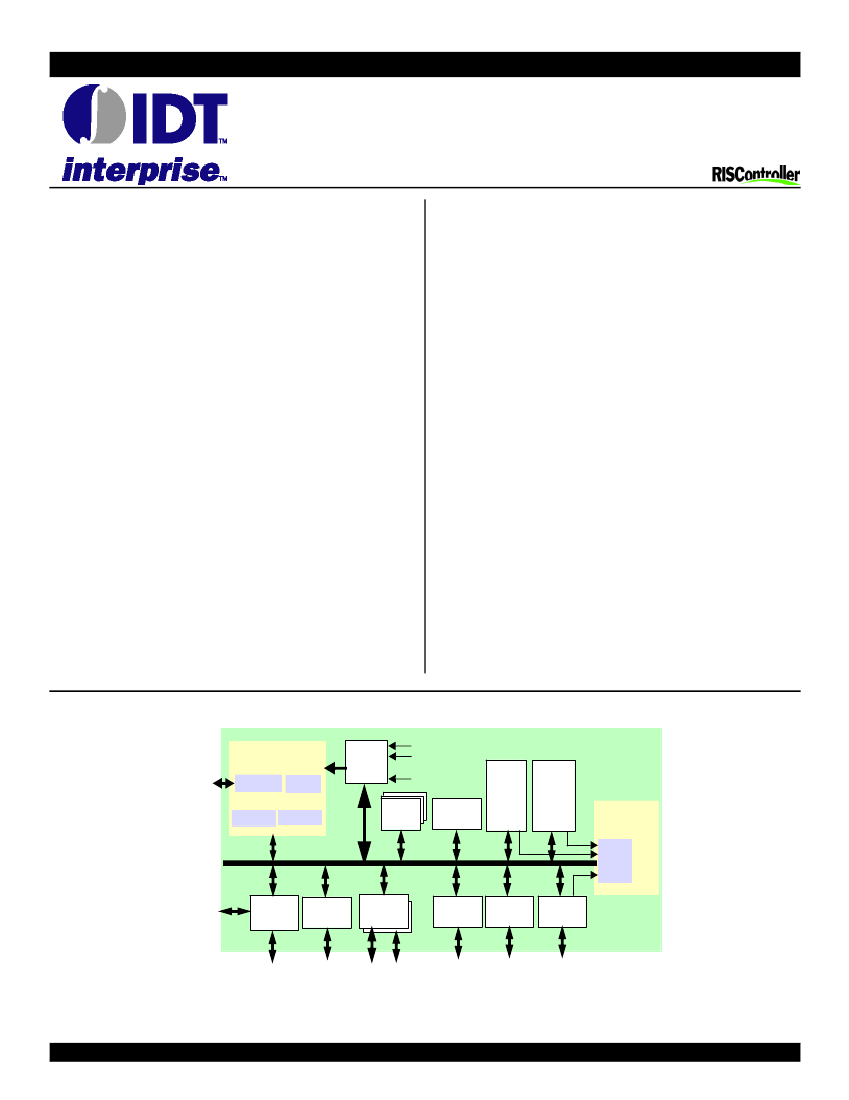

Block Diagram

RC32300

CPU Core

ICE

EJTAG

D. Cache

MMU

I. Cache

3 Counter

Timers

Watchdog

Timer

Interrupt

Controller

:

:

10/100

Ethernet

Interface

USB

Interface

16 Channel

DMA

Controller

Arbiter

Ext. Bus

Master

SDRAM &

Device

Controller

I

2

C

Controller

2 UARTS

(16550)

GPIO

Interface

TDM

Interface

ATM

Interface

Memory &

Peripheral Bus

I

2

C Bus

Ch. 1 Ch. 2

Serial Channels

GPIO Pins

TDM Bus

Utopia 1 / 2

Figure 1 RC32355 Internal Block Diagram

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

1 of 47

漏

2004 Integrated Device Technology, Inc.

May 25, 2004

DSC 5900