铮?/div>

Mobile 133.3MHz Chipset

Three CPU Clocks (66.6/100/133.3 MHz, 2.5V)

Six SDRAM Clocks, 1-DCLK (100/133.3 MHz, 3.3V)

Seven PCI Clocks (33MHz, 3.3V), one free running

Two IOAPIC clocks, synchronous to CPU clock (33.3

MHz, 2.5V)

鈥?One REF Clock

鈥?Two 48-MHz fixed non-SSCG clocks (USB and DOT)

鈥?Three 3V66 clocks (66.6 MHz, 3.3V) ICH, HUBLINK, and

AGP memory

鈥?One selectable frequency for VCH video channel clock

(48-MHz non-SSCG, 66.6-MHz CPU-SSCG, 3.3V)

鈥?Power management using power-down, CPU stop, and

PCI stop pins

鈥?Three function select pins (include test-mode select)

鈥?Cypress Spread Spectrum for best electromagnetic

interference (EMI) reduction

鈥?SMBUS support with readback

鈥?56-pin SSOP and TSSOP packages

Table 1. Function Table

[1]

TEST#

0

0

1

1

1

1

SEL1

X

X

0

0

1

1

SEL0

0

1

0

1

0

1

CPU(0:2)

Hi-Z

TCLK/2

66.6

100.0

133.3

133.3

SDRAM(0:5)

DCLK

Hi-Z

TCLK/2

100.0

[2]

3V66(0:2)

Hi-Z

TCLK/3

66.6

66.6

66.6

66.6

PCIF(1:6)

Hi-Z

TCLK/6

33.3

33.3

33.3

33.3

48M(0:1)

Hi-Z

TCLK/2

48

48

48

48

REF

Hi-Z

TCLK

14.318

14.318

14.318

14.318

IOAPIC(0:10)

Hi-Z

TCLK/6

33.3

33.3

33.3

33.3

100.0

[2]

133.3

100.0

[2]

Note:

1. These are the frequencies that are selectable after power up using the SEL1 and SEL0 hardware pins. Other frequencies may be chosen using the devices

SMBUS interface. See the expanded frequency for a complete listing of all of the availible frequencies.

2. Will be set to 133MHz, when SMBUS Byte3, Bit 0 is set to logic 1.

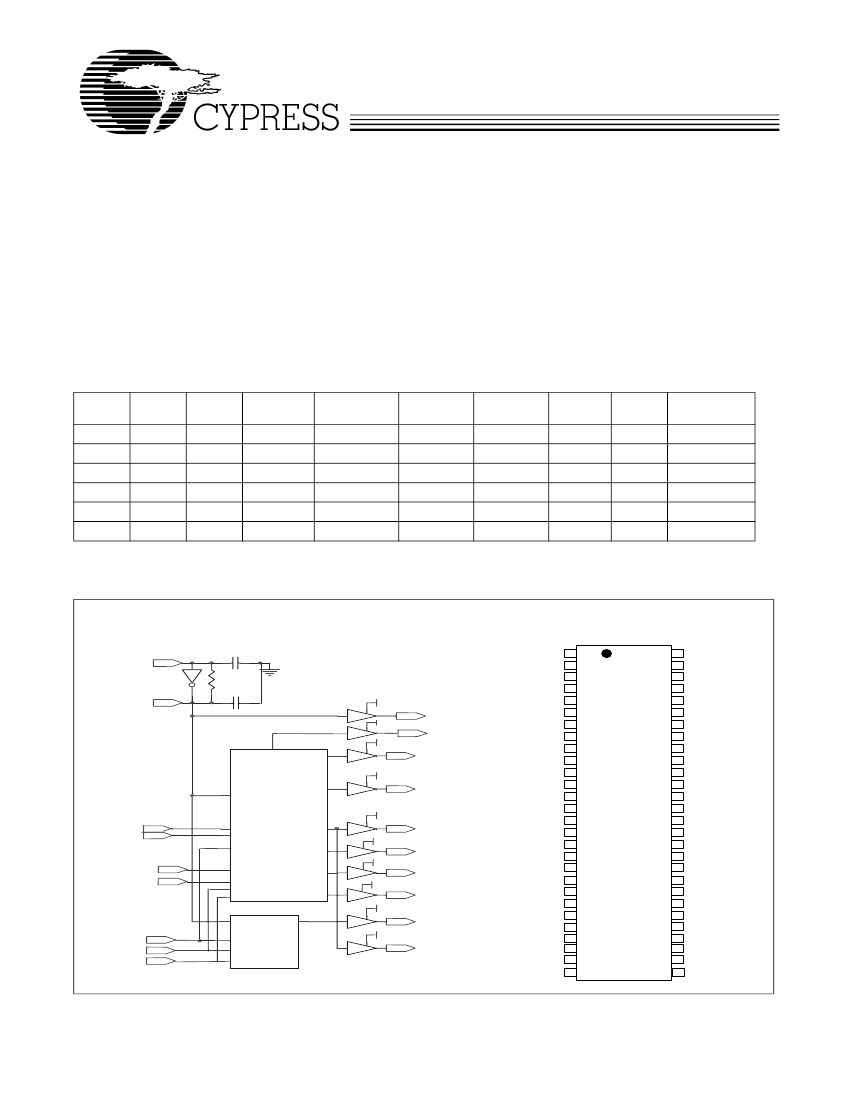

Block Diagram

X IN

36pF

Pin Configuration

REF

VDD

XIN

XO U T

VSS

VSS

3V 66_0

3V 66_1

3V 66_2(A G P )

VDD

P C I_S TP #

P C I_F

P C I1

VSS

P C I2

P C I3

VDDP

P C I4

P C I5

P C I6

VSS

AVDD

AVSS

VSS

48M 0(U S B )

48M 1(D O T)

VDD

S E L0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

VSS

IO A P IC 0

IO A P IC 1

VDDI

CPU0

VDDC

CPU1

CPU2

VSS

VSS

SDRAM0

SDRAM1

VDDS

SDRAM2

SDRAM3

VSS

SDRAM4

SDRAM5

D C LK

VDDS

V C H _C LK

VDD

C P U _S TP #

TE S T #

PD#

S C LK

S D A TA

S E L1

36pF

XOUT

1

VDD

1

VDDI

IO A P IC

2

VDDC

CPU

R in

VDDS

TEST#

S E L 0 ,1

tris ta te

s0

PD#

P C I_ S T P #

C PU _STP#

i2 c - c lk

i2 c - d a ta

PLL1

R in

PD#

SC LK

SDATA

i2 c -c lk

i2 c -d a t a

PLL2

PD#

1

D C LK

48

2

VDDS

PCI

6

VDD

4 8 M (0 ,1 )

VDDP

P C I(1 :6 )

SDRAM

6

VDD

3V66

3

VDDP

P C I_ F

3 V 6 6 (0 :2 )

S D R A M ( 0 :5 )

3

C P U (0 :2 )

IO A P IC ( 0 ,1 )

V C H _C LK

VDD

REF

C

9

8

3

5

Cypress Semiconductor Corporation

Document #: 38-07303 Rev. **

鈥?/div>

3901 North First Street

鈥?/div>

San Jose

鈥?/div>

CA 95134

鈥?408-943-2600

Revised April 5, 2002