MC10EP31, MC100EP31

3.3V / 5V ECL D Flip-Flop

with Set and Reset

The MC10/100EP31 is a D flip鈥揻lop with set and reset. The device

is pin and functionally equivalent to the EL31 and LVEL31 devices.

With AC performance much faster than the EL31 and LVEL31

devices, the EP31 is ideal for applications requiring the fastest AC

performance available. Both set and reset inputs are asynchronous,

level triggered signals. Data enters the master portion of the flip鈥揻lop

when CLK is low and is transferred to the slave, and thus the outputs,

upon a positive transition of the CLK.

The 100 Series contains temperature compensation.

http://onsemi.com

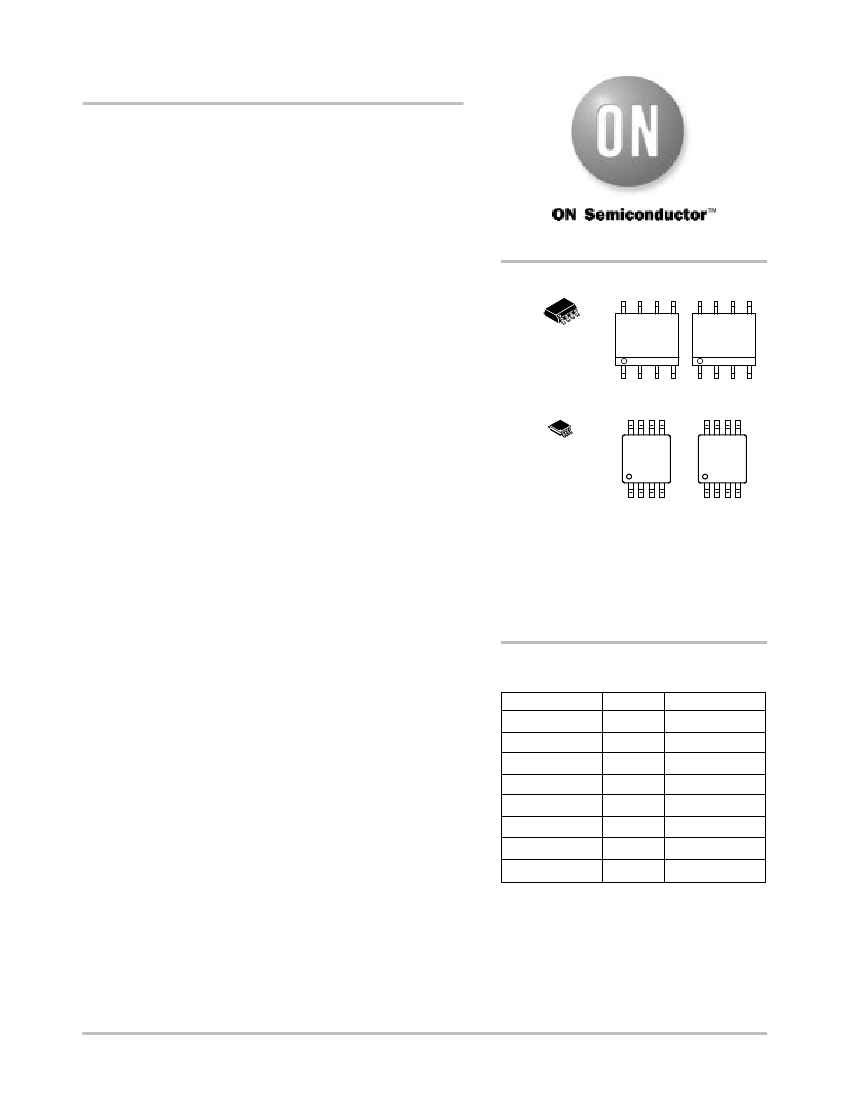

MARKING DIAGRAMS*

8

8

1

SO鈥?

D SUFFIX

CASE 751

HEP31

ALYW

1

1

KEP31

ALYW

8

鈥?/div>

340 ps Typical Propagation Delay

鈥?/div>

Maximum Frequency > 3 GHz Typical

鈥?/div>

PECL Mode Operating Range: V

CC

= 3.0 V to 5.5 V

with V

EE

= 0 V

鈥?/div>

NECL Mode Operating Range: V

CC

= 0 V

with V

EE

= 鈥?.0 V to 鈥?.5 V

鈥?/div>

Open Input Default State

8

1

TSSOP鈥?

DT SUFFIX

CASE 948R

8

HP31

ALYW

1

8

KP31

ALYW

1

L = Wafer Lot

Y = Year

W = Work Week

鈥?/div>

Q Output Will Default LOW with Inputs Open or at V

EE

H = MC10

K = MC100

A = Assembly Location

*For additional information, see Application Note

AND8002/D

ORDERING INFORMATION

Device

MC10EP31D

MC10EP31DR2

MC100EP31D

MC100EP31DR2

MC10EP31DT

MC10EP31DTR2

MC100EP31DT

Package

SO鈥?

SO鈥?

SO鈥?

SO鈥?

TSSOP鈥?

TSSOP鈥?

TSSOP鈥?

Shipping

98 Units/Rail

2500 Tape & Reel

98 Units/Rail

2500 Tape & Reel

100 Units/Rail

2500 Tape & Reel

100 Units/Rail

2500 Tape & Reel

MC100EP31DTR2 TSSOP鈥?

漏

Semiconductor Components Industries, LLC, 2001

1

April, 2001 鈥?Rev. 5

Publication Order Number:

MC10EP31/D