700MHz min. count frequency

鈩?/div>

input pulldown resistors

s

Fully compatible with Motorola MC10E/100E016

s

Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E016 are high-speed synchronous,

presettable and cascadable 8-bit binary counters designed

for use in new, high-performance ECL systems. Architecture

and operation are the same as the Motorola MC10H016 in

the MECL 10KH family, extended to 8 bits, as shown in the

logic diagram.

The counters feature internal feedback of TC, gated by

the TCLD (terminal count load) pin. When TCLD is LOW,

the TC feedback is disabled and counting proceeds

continuously, with TC going LOW to indicate an all-HlGH

state. When TCLD is HIGH, the TC feedback causes the

counter to automatically reload upon TC = LOW, thus

functioning as a programmable counter.

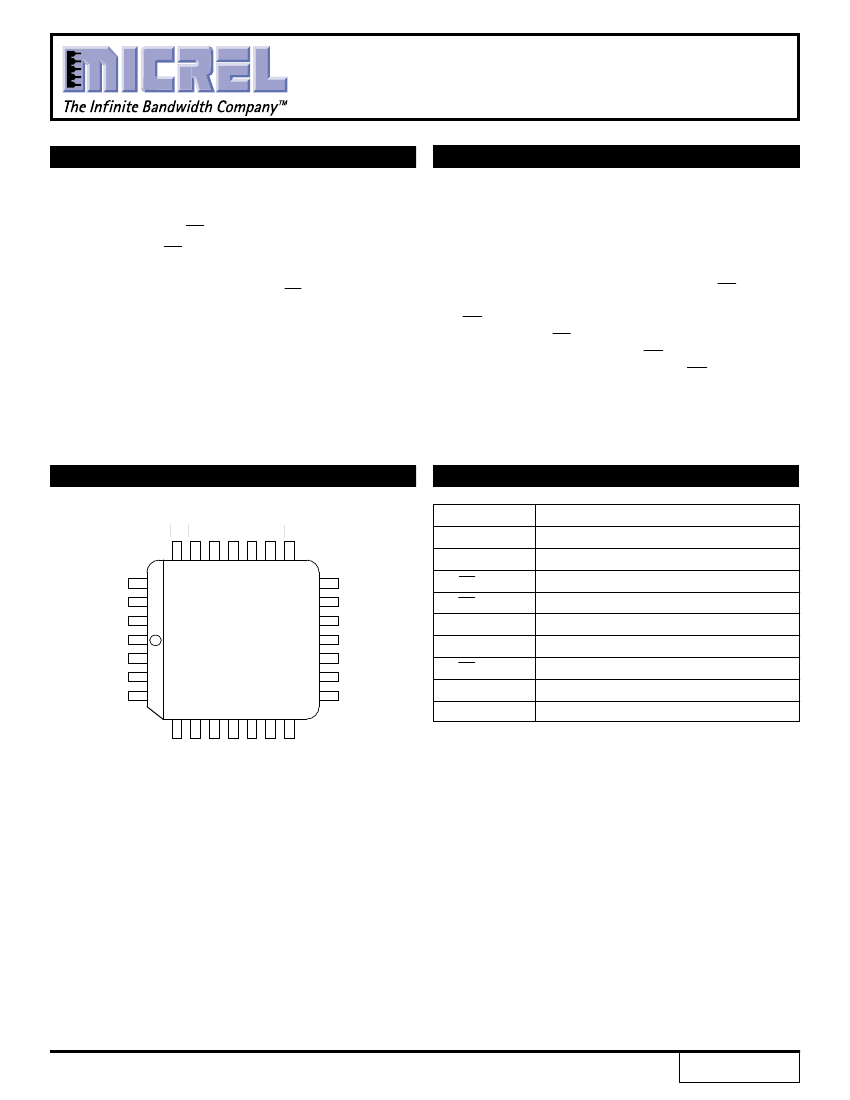

PIN CONFIGURATION

V

CCO

PE

CE

P

7

P

6

P

5

TC

PIN NAMES

Pin

P

0

-P

7

Q

0

-Q

7

18

17

Function

Parallel Data (Preset) Inputs

Data outputs

Count Enable Control Input

Parallel Load Enable Control Input

Master Reset

Clock

Terminal Count Output

TC-Load Control Input

V

CC

to Output

25 24 23 22 21 20 19

MR

CLK

TCLD

V

EE

NC

P

0

P

1

26

27

28

1

2

3

4

5

6

7

8

9

10 11

Q

7

Q

6

V

CC

Q

5

V

CCO

Q

4

Q

3

CE

PE

MR

CLK

TC

TCLD

V

CCO

PLCC

TOP VIEW

J28-1

16

15

14

13

12

P

2

P

3

P

4

V

CCO

Q

0

Q

1

Q

2

Rev.: D

Amendment: /2

1

Issue Date: May, 1998