鈻?/div>

Available in 32-pin EPAD-TQFP and 28-pin SOIC

packages (28-pin SOIC is available, but is not

recommended for new designs.)

DESCRIPTION

The SY87700L is a complete Clock Recovery and Data

Retiming integrated circuit for data rates from 32Mbps

up to 175Mbps NRZ. The device is ideally suited for

SONET/SDH/ATM applications and other high-speed data

transmission systems.

Clock recovery and data retiming is performed by

synchronizing the on-chip VCO directly to the incoming

data stream. The VCO center frequency is controlled by

the reference clock frequency and the selected divide

ratio. On-chip clock generation is performed through the

use of a frequency multiplier PLL with a byte rate source

as reference.

The SY87700L also includes a link fault detection

circuit.

All support documentation can be found on Micrel鈥檚 web

site at: www.micrel.com.

APPLICATIONS

鈻?/div>

SONET/SDH/ATM OC-1 and OC-3

鈻?/div>

Fast Ethernet, SMPTE 259

鈻?/div>

Proprietary architecture up to 175Mbps

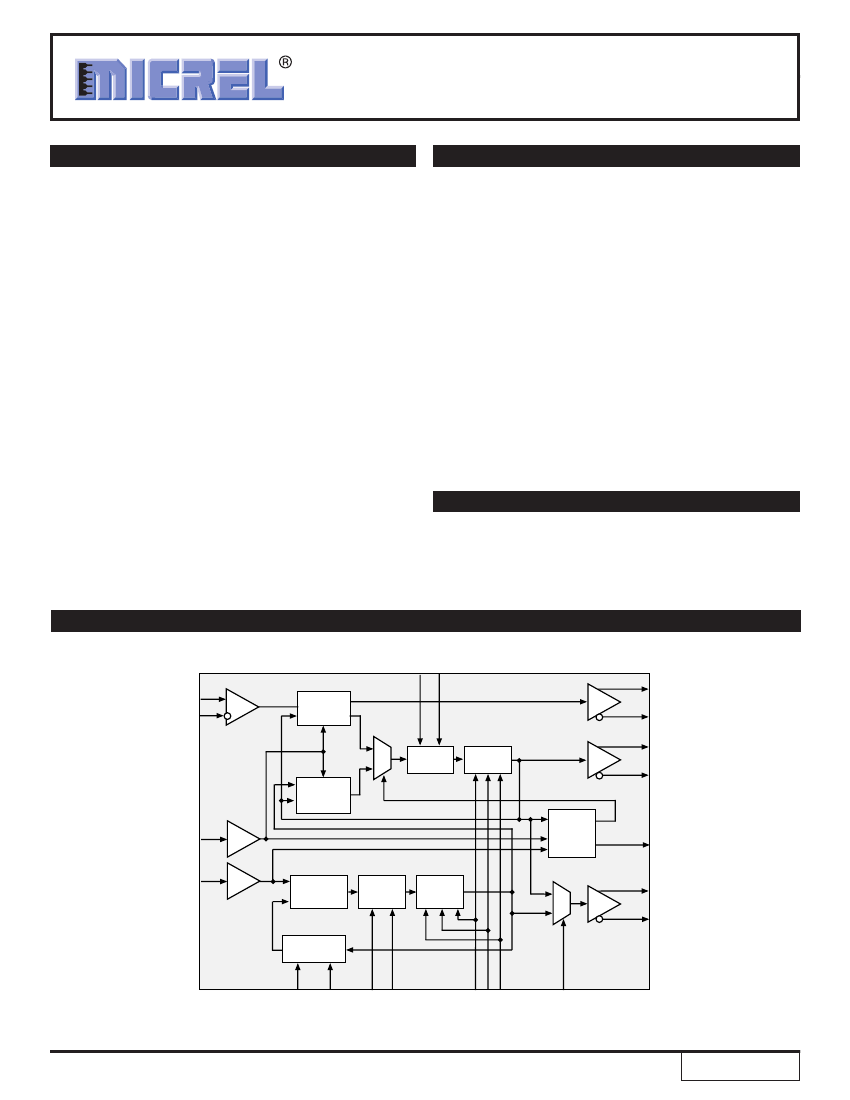

BLOCK DIAGRAM

PLLR P/N

RDOUTP

(PECL)

RDOUTN

0

1

PHASE/

FREQUENCY

DETECTOR

LINK

FAULT

DETECTOR

RDINP

(PECL)

RDINN

PHASE

DETECTOR

CHARGE

PUMP

VCO

RCLKP

(PECL)

RCLKN

CD

(PECL)

REFCLK

(TTL)

LFIN

(TTL)

PHASE/

FREQUENCY

DETECTOR

CHARGE

PUMP

VCO

1

0

TCLKP

(PECL)

TCLKN

DIVIDER

BY 8, 10, 16, 20

SY87700L

DIVSEL 1/2

(TTL)

PLLS P/N

FREQSEL 1/2/3

(TTL)

CLKSEL

(TTL)

V

CC

V

CCA

V

CCO

GND

AnyRate is a registered trademark of Micrel, Inc.

M9999-111406

hbwhelp@micrel.com or (408) 955-1690

Rev.: H

Amendment: /0

1

Issue Date: September 2006