Philips Semiconductors

SC16C654B/654DB

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 64-byte FIFOs

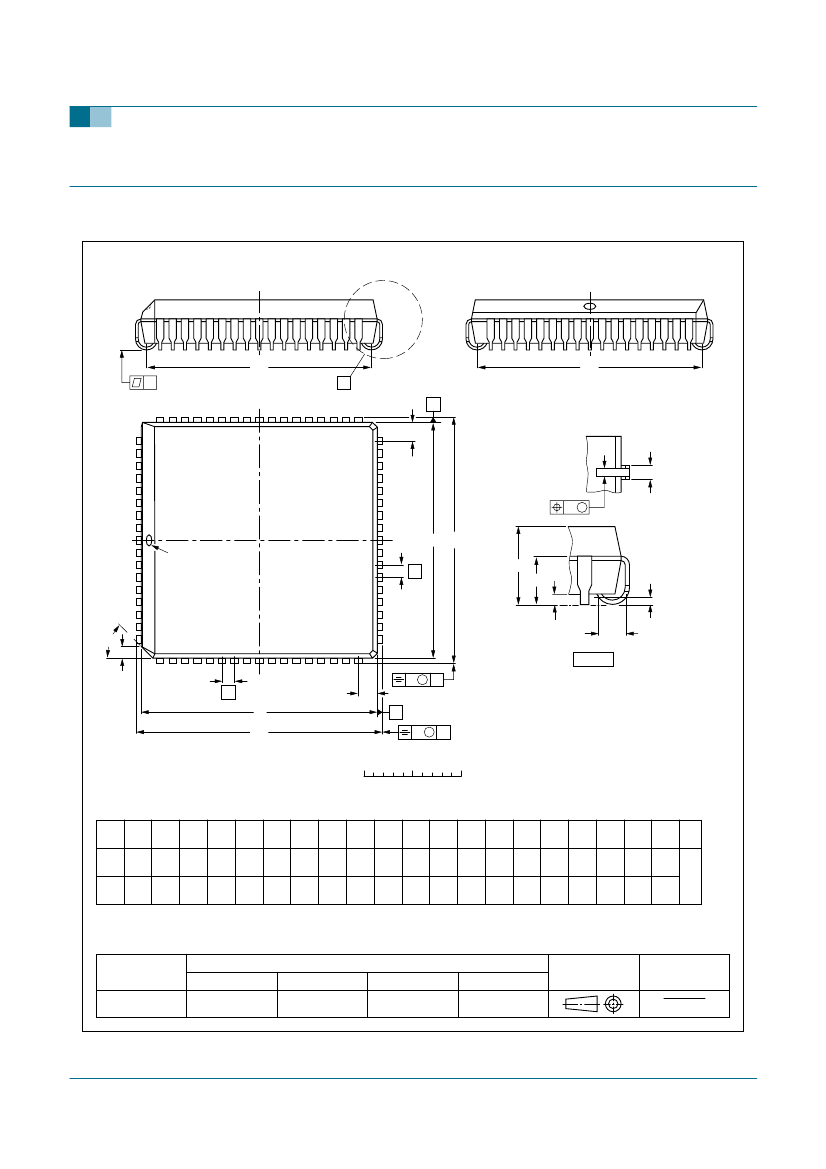

11. Package outline

PLCC68: plastic leaded chip carrier; 68 leads

SOT188-2

eD

y

60

61

X

44

43 Z E

A

eE

b

p

b

1

w

M

68

1

pin 1 index

e

E

HE

A

A

4

A

1

(A

3

)

L

p

detail X

尾

k

9

27

10

e

D

HD

26

ZD

B

v

M

A

v

M

B

0

5

scale

10 mm

DIMENSIONS (mm dimensions are derived from the original inch dimensions)

A4

A1

UNIT A

D

(1)

E

(1)

e

A3

eD

eE

HD

bp b1

max.

min.

mm

inches

4.57

4.19

0.51

0.25

0.01

3.3

0.13

0.53

0.33

0.81

0.66

HE

k

Lp

1.44

1.02

v

0.18

w

0.18

y

0.1

ZD

(1)

ZE

(1)

max. max.

2.16

2.16

尾

23.62 23.62 25.27 25.27 1.22

24.33 24.33

1.27

22.61 22.61 25.02 25.02 1.07

24.13 24.13

0.93

0.89

0.93

0.89

45

o

0.180

0.02

0.165

0.021 0.032 0.958 0.958

0.05

0.013 0.026 0.950 0.950

0.995 0.995 0.048 0.057

0.007 0.007 0.004 0.085 0.085

0.985 0.985 0.042 0.040

Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

OUTLINE

VERSION

SOT188-2

REFERENCES

IEC

112E10

JEDEC

MS-018

JEITA

EDR-7319

EUROPEAN

PROJECTION

ISSUE DATE

99-12-27

01-11-14

Fig 27. Package outline SOT188-2 (PLCC68)

9397 750 14965

漏 Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 02 鈥?20 June 2005

48 of 58