A82DL32x4T(U) Series

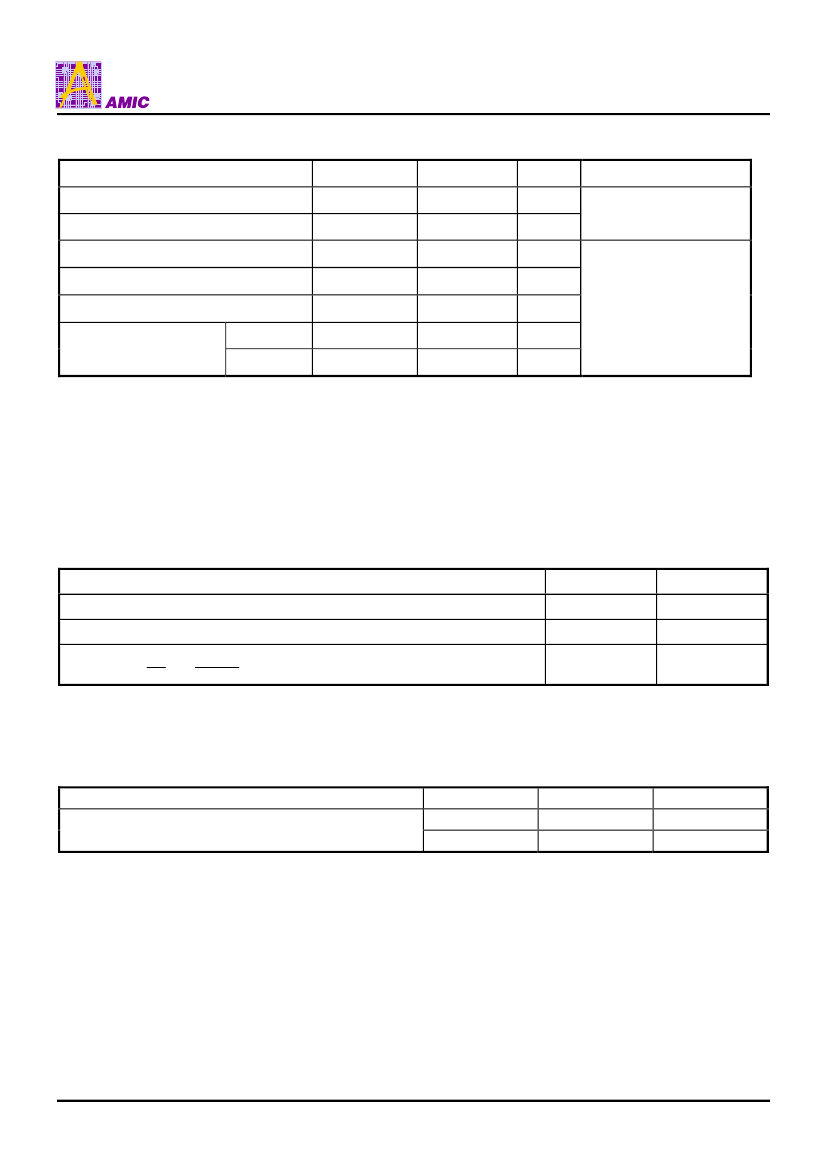

ERASE AND PROGRAMMING PERFORMANCE

Parameter

Sector Erase Time

Chip Erase Time

Byte Programming Time

Word Programming Time

Accelerated Word/Byte Programming Time

Chip Programming Time

(Note 3)

Byte Mode

Word Mode

Typ. (Note 1)

0.7

27

5

7

4

9

6

150

210

120

27

18

Max. (Note 2)

15

Unit

sec

sec

碌

s

碌

s

碌

s

Comments

Excludes 00h programming

prior to erasure (Note 4)

Excludes system-level

overhead (Note 5)

sec

sec

Notes:

1. Typical program and erase times assume the following conditions: 25

掳

C, 3.0V VCC_F, 10,000 cycles. Additionally,

programming typically assumes checkerboard pattern.

2. Under worst case conditions of 90

掳

C, VCC_F = 2.7V, 100,000 cycles.

3. The typical chip programming time is considerably less than the maximum chip programming time listed, since most bytes

program faster than the maximum byte program time listed.

4. In the pre-programming step of the Embedded Erase algorithm, all bytes are programmed to 00h before erasure.

5. System-level overhead is the time required to execute the four-bus-cycle command sequence for programming. See Table 12

for further information on command definitions.

6. The device has a minimum erase and program cycle endurance of 10,000 cycles.

FLASH LATCH-UP CHARACTERISTICS

Description

Input Voltage with respect to VSS on all I/O pins

VCC_F Current

Input voltage with respect to VSS on all pins except I/O pins

(including A9,

OE

and

RESET

)

Includes all pins except VCC_F. Test conditions: VCC_F = 3.0V, one pin at time.

Min.

-1.0V

-100 mA

-1.0V

Max.

VCC_F+1.0V

+100 mA

12.5V

DATA RETENTION

Parameter

Minimum Pattern Data Retention Time

Test Conditions

150

掳

C

125

掳

C

Min

10

20

Unit

Years

Years

PRELIMINARY

(August, 2005, Version 0.0)

56

AMIC Technology, Corp.