SN65LV1023A/SN65LV1224A

10-MHz TO 66-MHz, 10:1 LVDS SERIALIZER/DESERIALIZER

SLLS570A 鈥?JUNE 2003 鈥?REVISED JUNE 2003

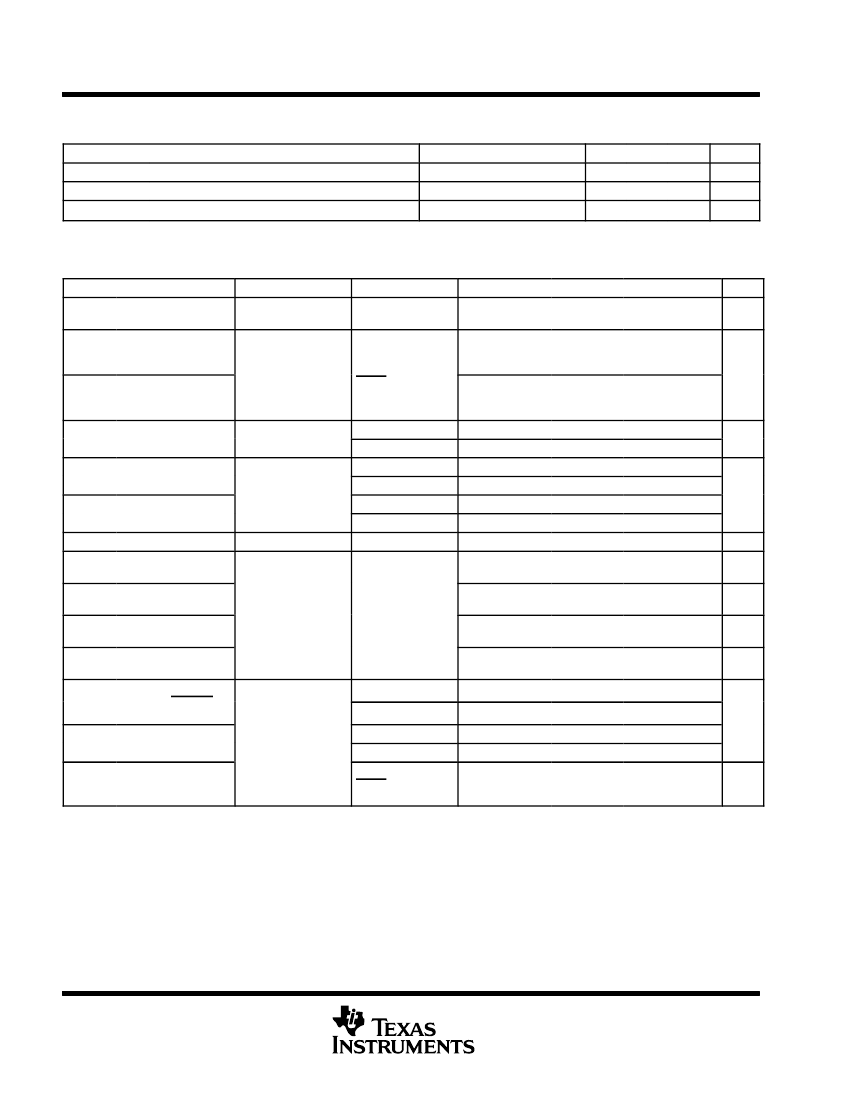

deserializer timing requirements for REFCLK over recommended operating supply and

temperature ranges (unless otherwise specified)

PARAMETER

tRFCP

tRFDC

tt(RF)

REFCLK period

REFCLK duty cycle

REFCLK transition time

TEST CONDITIONS

MIN

15.15

30%

TYP

T

50%

3

MAX

100

70%

6

ns

UNIT

ns

deserializer switching characteristics over recommended operating supply and temperature

ranges (unless otherwise specified)

PARAMETER

t(RCP)

tTLH(C)

Receiver out clock

period

CMOS/TTL

low-to-high transition

time

CMOS/TTL

high-to-low transition

time

Deserializer delay,

See Figure 13

ROUTx data valid

before RCLK

See Figure 14

t(ROH)

t(RDC)

td(HZ)

td(LZ)

td(HR)

td(ZL)

t(DSR1)

ROUTx data valid

after RCLK

RCLK duty cycle

High-to-high-impedan

ce state delay

Low-to-high-impedan

ce state delay

High-impedance

state-to-high delay

High-impedance-stat

e-to-low delay

Deserializer PLL lock

time from PWRDN

(with SYNCPAT)

Deserializer PLL lock

time from SYNCPAT

High-impedance-stat

e to-high delay

(power up)

See Figure 16,

Figure 17, and

17

Note 7

10 MHz

66 MHz

10 MHz

66 MHz

LOCK

See Figure 15

ROUT0 鈥?ROUT9

5.3

4.7

8

8

815 x tRFCP

815 x tRFCP

0.7

0.2

3

ns

碌s

ns

ns

TEST CONDITIONS

t(RCP) = t(TCP),

See Figure 12

PIN/FREQ

RCLK

MIN

15.15

TYP

MAX

100

UNIT

ns

1.2

CL = 15 pF,

F,

See Figure 6

ROUT0 鈥?ROUT9,

LOCK, RCLK

1.1

Room tem erature,

temperature,

3.3 V

10 MHz

66 MHz

RCLK 10 MHz

RCLK 66 MHz

10 MHz

66 MHz

1.75脳tRCP+4.2

1.75脳tRCP+7.4

0.4脳tRCP

0.4脳tRCP

鈥?0.4脳tRCP

鈥?0.4脳tRCP

40%

0.5脳tRCP

0.5脳tRCP

鈥?0.5脳tRCP

鈥?0.5脳tRCP

50%

6.5

4.7

2.5

ns

2.5

1.75脳tRCP +12.6

1.75脳tRCP +9.7

tTHL(C)

td(D)鈥?/div>

t(ROS)

ns

ns

60%

8

8

ns

ns

t(DSR2)

td(ZHLK)

鈥?The deserializer delay time for all frequencies does not exceed 2 serial bit times.

NOTE 7: t(DSR1) represents the time required for the deserializer to register that a lock has occurred upon powerup or when leaving the

powerdown mode. t(DSR2) represents the time required to register that a lock has occurred for the powered up and enabled deserializer

when the input (RI卤) conditions change from not receiving data to receiving synchronization patterns (SYNCPATs). In order to specify

deserializer PLL performance tDSR1 and tDSR2 are specified with REFCLK active and stable and specific conditions of SYNCPATs.

10

POST OFFICE BOX 655303

鈥?/div>

DALLAS, TEXAS 75265