dsPIC30F6011/6012/6013/6014

4.0

ADDRESS GENERATOR UNITS

4.1

Instruction Addressing Modes

The dsPIC core contains two independent address

generator units: the X AGU and Y AGU. The Y AGU

supports word sized data reads for the DSP

MAC

class

of instructions only. The dsPIC30F AGUs support:

鈥?Linear Addressing

鈥?Modulo (Circular) Addressing

鈥?Bit-Reversed Addressing

Linear and Modulo Data Addressing modes can be

applied to data space or program space. Bit-reversed

addressing is only applicable to data space addresses.

The Addressing modes in Table 4-1 form the basis of

the Addressing modes optimized to support the specific

features of individual instructions. The Addressing

modes provided in the

MAC

class of instructions are

somewhat different from those in the other instruction

types.

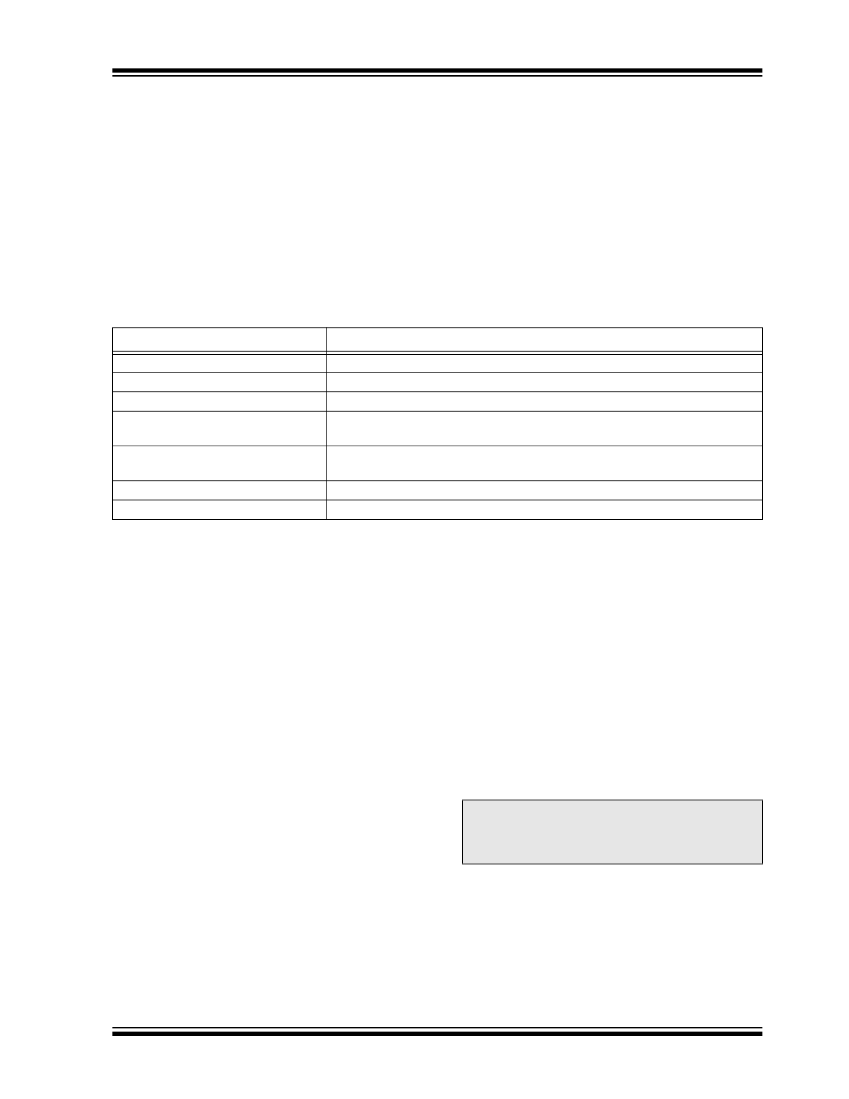

TABLE 4-1:

FUNDAMENTAL ADDRESSING MODES SUPPORTED

Description

The address of the File register is specified explicitly.

The contents of a register are accessed directly.

The contents of Wn forms the EA.

The contents of Wn forms the EA. Wn is post-modified (incremented or

decremented) by a constant value.

Wn is pre-modified (incremented or decremented) by a signed constant value

to form the EA.

The sum of Wn and a literal forms the EA.

Addressing Mode

File Register Direct

Register Direct

Register Indirect

Register Indirect Post-modified

Register Indirect Pre-modified

Register Indirect with Register Offset The sum of Wn and Wb forms the EA.

Register Indirect with Literal Offset

4.1.1

FILE REGISTER INSTRUCTIONS

4.1.2

MCU INSTRUCTIONS

Most File register instructions use a 13-bit address field

(f) to directly address data present in the first 8192

bytes of data memory (Near data space). Most File

register instructions employ a working register, W0,

which is denoted as WREG in these instructions. The

destination is typically either the same File register or

WREG (with the exception of the

MUL

instruction),

which writes the result to a register or register pair. The

MOV

instruction allows additional flexibility and can

access the entire data space.

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (i.e., the

Addressing mode can only be register direct) which is

referred to as Wb. Operand 2 can be a W register,

fetched from data memory or a 5-bit literal. The result

location can be either a W register or a data memory

location. The following addressing modes are

supported by MCU instructions:

鈥?/div>

鈥?/div>

鈥?/div>

鈥?/div>

鈥?/div>

Register Direct

Register Indirect

Register Indirect Post-modified

Register Indirect Pre-modified

5-bit or 10-bit Literal

Note:

Not all instructions support all the

Addressing modes given above. Individual

instructions may support different subsets

of these Addressing modes.

铮?/div>

2004 Microchip Technology Inc.

Preliminary

DS70117C-page 37

DSPIC30F6011AT-20E/S相关型号PDF文件下载

-

型号

版本

描述

厂商

下载

-

英文版

Serial Peripheral Interface - Master/Slave

DCD

-

英文版

Serial Peripheral Interface - Slave

DCD

-

英文版

Flash Programming Specification

-

英文版

Flash Programming Specification

MICROCHIP ...

-

英文版

dsPIC High-Performance 16-bit Digital Signal Controller Fami...

-

英文版

dsPIC High-Performance 16-bit Digital Signal Controller Fami...

MICROCHIP ...

-

英文版

High-Performance, 16-bit Digital Signal Controllers

-

英文版

Serial Peripheral Interface Master/Slave with FIFO

DCD [Digit...

-

英文版

28/44-Pin High-Performance Switch Mode Power Supply Digital ...

-

英文版

28/44-Pin High-Performance Switch Mode Power Supply Digital ...

MICROCHIP ...

-

英文版

-

英文版

High-Performance Digital Signal Controllers

-

英文版

High-Performance Digital Signal Controllers

-

英文版

High-Performance Digital Signal Controllers

MICROCHIP ...

-

英文版

High-Performance Digital Signal Controllers

-

英文版

High-Performance Digital Signal Controllers

MICROCHIP ...

-

英文版

28/44-Pin High-Performance Switch Mode Power Supply Digital ...

-

英文版

-

英文版

44-Pin High-Performance Switch Mode Power Supply Digital Sig...

-

英文版

44-Pin High-Performance Switch Mode Power Supply Digital Sig...