鈼?/div>

ATM SAR

鈥?Can be configured as one UTOPIA level 1 interface or 1

UTOPIA level 2 interface with 2 address lines (3 PHYs max)

鈥?Supports 25Mb/s and faster ATM

鈥?Supports UTOPIA data path interface operation at speeds up

to 33 MHz

鈥?Supports standard 53-byte ATM cells

鈥?Performs HEC generation and checking

鈥?Cell processing discards short cells and clips long cells

鈥?16 cells worth of buffering

鈥?UTOPIA modes: 8 cell input buffer and 8 cell output buffer

鈥?Hardware support for CRC-32 generation and checking for

AAL5

鈥?Hardware support for CRC-10 generation and checking

鈥?Virtual caching receive mechanism supports reception of any

length packet without CPU intervention on up to eight simulta-

neously active receive channels

鈥?Frame Mode transmit mechanism supports transmission of

any length packet without CPU intervention

鈼?/div>

System Features

鈥?JTAG Interface (IEEE Std. 1149.1 compatible)

鈥?208 pin PQFP package

鈥?2.5V core supply and 3.3V I/O supply

鈥?Up to 180 MHz pipeline frequency and up to 75 MHz bus

frequency

鈼?/div>

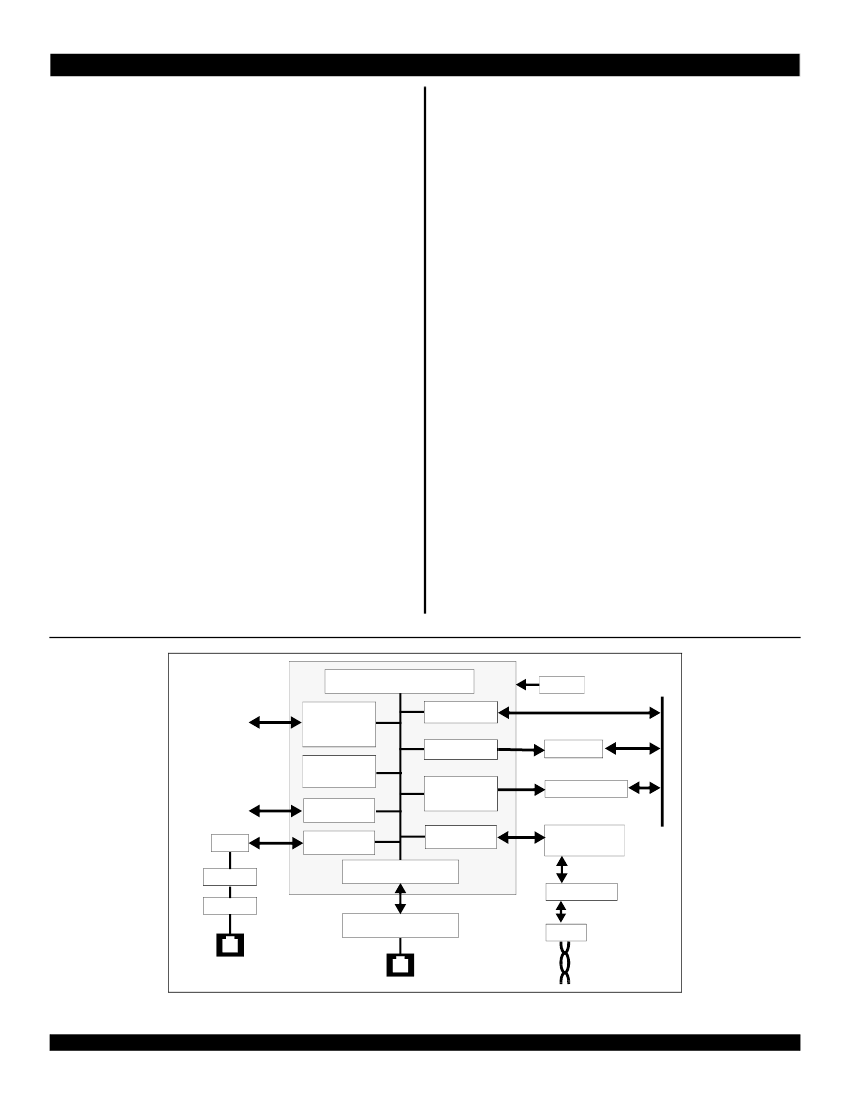

RC32300 CPU Core

Debug port

Timers

UART

Interrupt Ctl

DMA

Channels

USB to PC

Echo

Codec

SLIC

USB

TDM

Data Buffers

SDRAM Ctl

Memory &

I/O Controller

ATM I/F

Ethernet MAC

MII I/F

Ethernet Transceiver

POTS telephone

RJ11

Ethernet to PC

Clock

32-bit Data Bus

SDRAM

Memory & I/O

Transmission

Convergence

Data Pump

AFE

Figure 2 Example of xDSL Residential Gateway Using RC32355

2 of 47

May 25, 2004