EDX5116ABSE

Write Masking

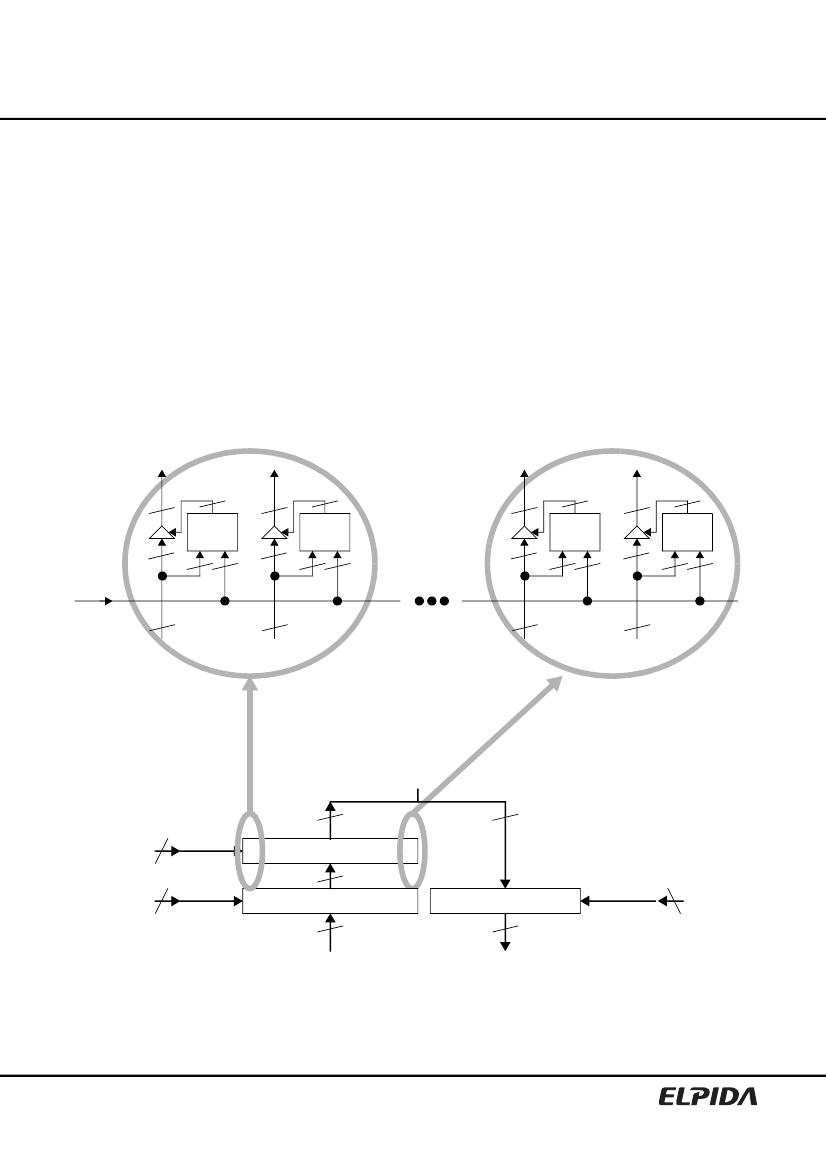

Figure 41 shows the logic used by the XDR DRAM device

when a write-masked command (WRM) is specified in a

COLM packet. This masking logic permits individual bytes of a

write data packet to be written or not written according to the

value of an eight bit write mask M[7:0].

In Figure 41, there are 16 sets of 16 bit signals forming the

D1[15:0][15:0] input bus for the Byte Mask block. These are

treated as 2x16 8-bit bytes:

D1[15][15:8]

D1[15][7:0]

...

D1[1][15:8]

D1[1][7:0]

D1[0][15:8]

Figure 41

Byte Mask Logic

S[15][7:0]

WE-MSB

[15]

1

NE

Compare

8

8

D1[15][15:8]

D1[0][7:0]

The eight bits of each byte is compared to the value in the byte

mask field (M[7:0]). If they are not equal (NE), then the corre-

sponding write enable signal (WE) is asserted and the byte is

written into the sense amplifier. If they are equal, then the cor-

responding write enable signal (WE) is deasserted and the byte

is not written into the sense amplifier.

In the example of Figure 41, a WRM command performs a

masked write of a 64 byte data packet to all the memory

devices connected to the RQ bus (and receiving the com-

mand). It is the job of the memory controller to search the 64

bytes to find an eight bit data value that is not used and place it

into the M[7:0] field. This will always be possible because there

are 256 possible 8-bit values and there are only 64 possible val-

ues used in the bytes in the data packet.

S[15][15:8]

S[0][15:8]

WE-LSB

[15]

1

NE

Compare

8

8

WE-MSB

[0]

1

NE

Compare

8

8

D1[0][15:8]

8

D1[0][15:8]

S[0][7:0]

WE-LSB

[0]

1

NE

Compare

8

8

D1[0][7:0]

8

D1[0][7:0]

8

8

8

8

8

8

8

8

M[7:0]

8

D1[15][7:0]

8

D1[15][7:0]

D1[15][15:8]

S[15:0][15:0]

16x16

8

M[7:0]

4+3

WIDTH[2:0]

SC[3:0]

Byte Mask (WR)

16x16

D1[15:0][15:0]

Dynamic Width Mux (RD)

16x16

Q[15:0][15:0]

4+3

WIDTH[2:0]

SC[3:0]

16x16

Dynamic Width Demux (WR)

16x16

D[15:0][15:0]

Note that other systems might use a data transfer size that is

different than the 64 bytes per t

CC

interval per RQ bus that is

used in the example in Figure 41.

Figure 42 shows the timing of two successive WRM com-

mands in COLM packets. The timing is identical to that of two

successive WR commands in COL packets. The one difference

Preliminary Data Sheet E0643E30 (Ver. 3.0)

52