EDX5116ABSE

RSL RQ Receive Timing

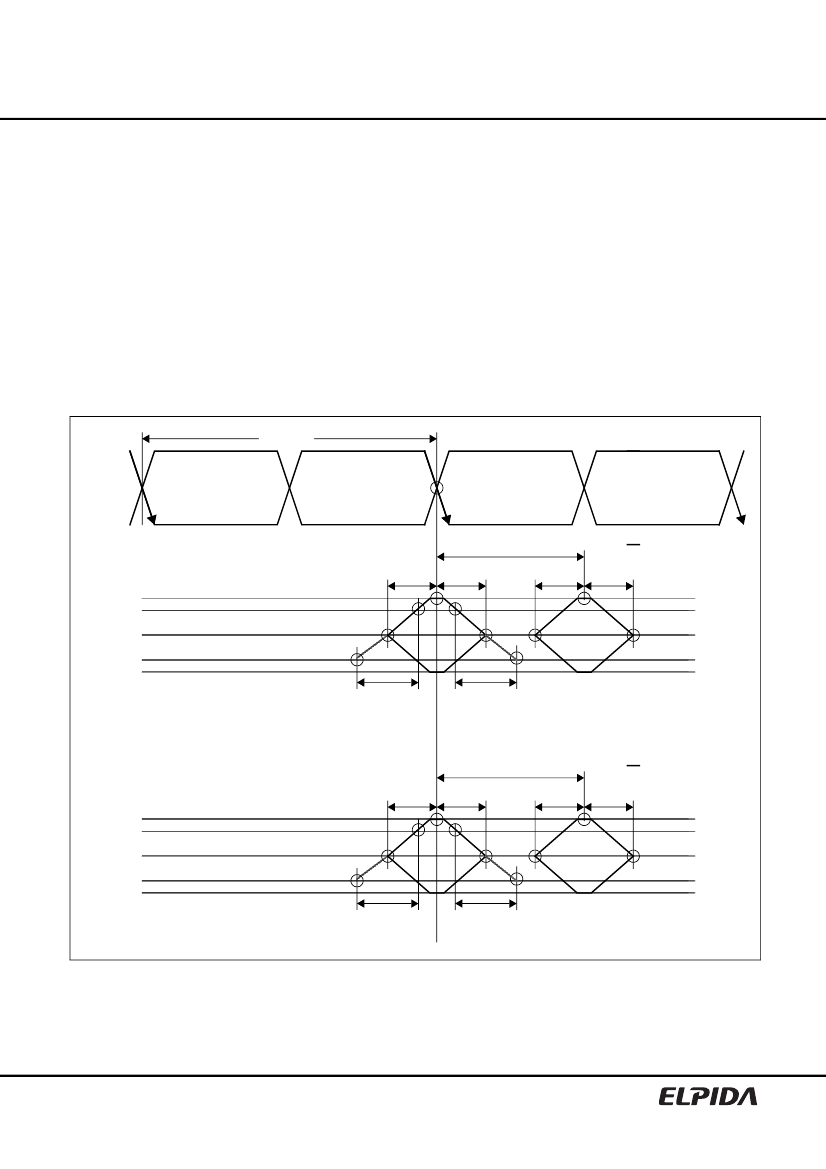

Figure 49 shows a timing diagram for the RQ11..0 request pins

of the memory component. This diagram represents a magni-

fied view of the pins and only a few clock cycles (CFM and

CFMN are the clock signals). Timing events are measured to

and from the primary CFM/CFMN crossing point in which

CFM makes its high-voltage-to-low-voltage transition. The

RQ11..0 signals are low-true: a high voltage represents a logical

zero and a low voltage represents a logical one. Timing events

on the RQ11..0 pins are measured to and from the point that

the signal reaches the level of the reference voltage V

REF,RSL

.

Because timing intervals are measured in this fashion, it is nec-

essary to constrain the slew rate of the signals. The rise (t

R,RQ

)

Figure 49

RSL RQ Receive Waveforms

and fall time (t

F,RQ

) of the signals are measured from the 20%

and 80% points of the full-swing levels.

20% = V

IL,RQ

+ 0.2*(V

IH,RQ

-V

IL,RQ

)

80% = V

IL,RQ

+ 0.8*(V

IH,RQ

-V

IL,RQ

)

There are two data receiving windows defined for each

RQ11..0 signal. The first of these (labeled 鈥?鈥? has a set time,

t

S,RQ

, and a hold time, t

H,RQ

, measured around the primary

CFM/CFMN crossing point. The second (labeled 鈥?鈥? has a

set time (t

S,RQ

) and a hold time (t

H,RQ

) measured around a

point 0.5*t

CYCLE

after the primary CFM/CFMN crossing

point.

t

CYCLE

CFM

CFMN

[1/2]鈥

CYCLE

t

S,RQ

t

H,RQ

t

S,RQ

t

H,RQ

logic 0

V

IH,RQ

80%

V

REF,RSL

20%

V

IL,RQ

logic1

RQ0

0

1

t

R,RQ

t

F,RQ

...

[1/2]鈥

CYCLE

t

S,RQ

t

H,RQ

t

S,RQ

t

H,RQ

logic 0

V

IH,RQ

80%

V

REF,RSL

20%

V

IL,RQ

logic 1

RQ11

0

1

t

R,RQ

t

F,RQ

Preliminary Data Sheet E0643E30 (Ver. 3.0)

65