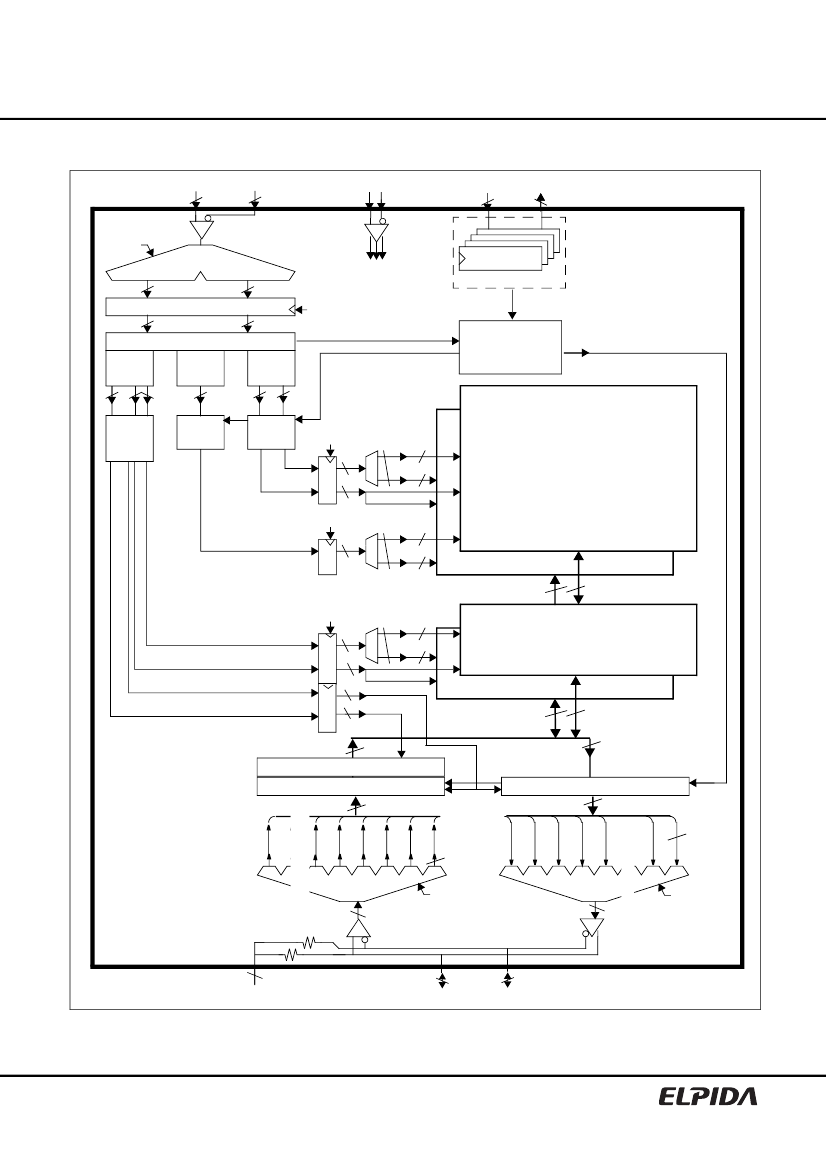

EDX5116ABSE

Figure 2

512Mb (8x4Mx16) XDR DRAM Block Diagram

RQ11..0

12

VREF

1

CFM CFMN

RST,SCK,CMD,SDI SDO

4

1

2/t

CYCLE

12

1:2 Demux

12

reg

12

Decode

1/t

CYCLE

1/t

CYCLE

2/t

CYCLE

16/ t

CC

Control Registers

12

COL logic

7

6+4

RD,WR

delay

{0..1}*t

CYCLE

PRE logic

3

3

PRE delay

{0..3}*t

CYCLE

ACT logic

12

3

REFB,REFr

Power Mode Logic

Calibration Logic

Refresh Logic

Initialization Logic

WIDTH

...

ACT delay

{0..1}*t

CYCLE

1/t

RR

3

12

1/t

PP

2

3

decode

1

...

ACT

ACT

ROW

ROW

Bank Array

Bank 0

16x16*2

6

*2

12

R,REFr

reg

BA,BR,REFB

1

2

3

decode

1

1

PRE

BP,BR,REFB

reg

3

...

PRE

Bank 0

16x16*2

6

1/t

CC

reg

BC

C

reg

SC

M

16x16

Byte Mask (WR)

Dynamic Width Demux (WR)

16x16

D[15:0][15:0]

...

...

Bank

(2

3

- 1)

16x16*2

6

...

2

3

decode

1

1

...

R/W

R/W

COL

COL

Sense Amp Array

16x16*2

6

Sense Amp 0

3

6

4

8

...

Sense Amp

(2

3

- 1)

...

16x16

Q[15:0][15:0]

16x16

16x16

WIDTH

S[15:0][15:0]

Dynamic Width Mux (RD)

16x16

16

16/t

CC

16

termination

16

2

VTERM

16

DQ15..0

16

DQN15..0

Preliminary Data Sheet E0643E30 (Ver. 3.0)

9

...

1:16 Demux

16:1 Mux

...

16

...

...

16/t

CC