ST7232A

16-BIT TIMER

(Cont鈥檇)

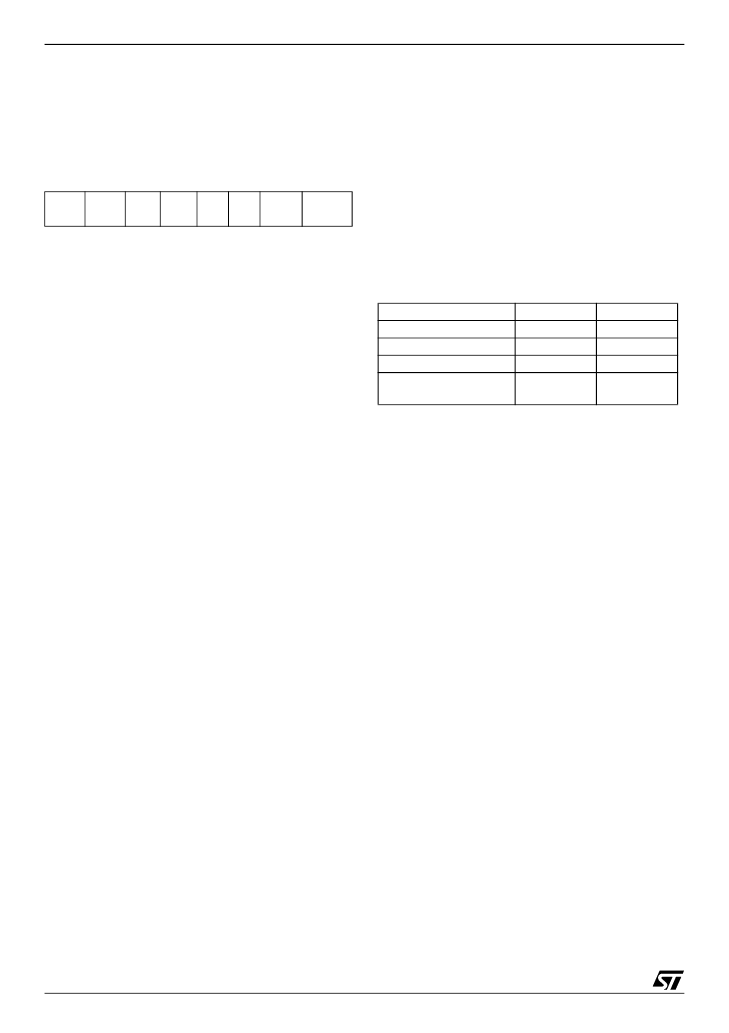

CONTROL REGISTER 2 (CR2)

Read/Write

Reset Value: 0000 0000 (00h)

7

0

OC1E OC2E OPM PWM CC1 CC0 IEDG2 EXEDG

Bit 4 =

PWM

Pulse Width Modulation.

0: PWM mode is not active.

1: PWM mode is active, the OCMP1 pin outputs a

programmable cyclic signal; the length of the

pulse depends on the value of OC1R register;

the period depends on the value of OC2R regis-

ter.

Bit 3, 2 =

CC[1:0]

Clock Control.

The timer clock mode depends on these bits:

Table 16. Clock Control Bits

Timer Clock

f

CPU

/ 4

f

CPU

/ 2

f

CPU

/ 8

External Clock (where

available)

CC1

0

0

1

1

CC0

0

1

0

1

Bit 7 =

OC1E

Output Compare 1 Pin Enable.

This bit is used only to output the signal from the

timer on the OCMP1 pin (OLV1 in Output Com-

pare mode, both OLV1 and OLV2 in PWM and

one-pulse mode). Whatever the value of the OC1E

bit, the Output Compare 1 function of the timer re-

mains active.

0: OCMP1 pin alternate function disabled (I/O pin

free for general-purpose I/O).

1: OCMP1 pin alternate function enabled.

Bit 6 =

OC2E

Output Compare 2 Pin Enable.

This bit is used only to output the signal from the

timer on the OCMP2 pin (OLV2 in Output Com-

pare mode). Whatever the value of the OC2E bit,

the Output Compare 2 function of the timer re-

mains active.

0: OCMP2 pin alternate function disabled (I/O pin

free for general-purpose I/O).

1: OCMP2 pin alternate function enabled.

Bit 5 =

OPM

One Pulse Mode.

0: One Pulse Mode is not active.

1: One Pulse Mode is active, the ICAP1 pin can be

used to trigger one pulse on the OCMP1 pin; the

active transition is given by the IEDG1 bit. The

length of the generated pulse depends on the

contents of the OC1R register.

Note:

If the external clock pin is not available, pro-

gramming the external clock configuration stops

the counter.

Bit 1 =

IEDG2

Input Edge 2.

This bit determines which type of level transition

on the ICAP2 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

Bit 0 =

EXEDG

External Clock Edge.

This bit determines which type of level transition

on the external clock pin EXTCLK will trigger the

counter register.

0: A falling edge triggers the counter register.

1: A rising edge triggers the counter register.

68/154

1