ST7232A

SERIAL PERIPHERAL INTERFACE

(Cont鈥檇)

10.4.3.2 Slave Select Management

As an alternative to using the SS pin to control the

Slave Select signal, the application can choose to

manage the Slave Select signal by software. This

is configured by the SSM bit in the SPICSR regis-

ter (see

Figure 46)

In software management, the external SS pin is

free for other application uses and the internal SS

signal level is driven by writing to the SSI bit in the

SPICSR register.

In Master mode:

鈥?SS internal must be held high continuously

In Slave Mode:

There are two cases depending on the data/clock

timing relationship (see

Figure 45):

If CPHA=1 (data latched on 2nd clock edge):

鈥?SS internal must be held low during the entire

transmission. This implies that in single slave

applications the SS pin either can be tied to

V

SS

, or made free for standard I/O by manag-

ing the SS function by software (SSM= 1 and

SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

鈥?SS internal must be held low during byte

transmission and pulled high between each

byte to allow the slave to write to the shift reg-

ister. If SS is not pulled high, a Write Collision

error will occur when the slave writes to the

shift register (see

Section 10.4.5.3).

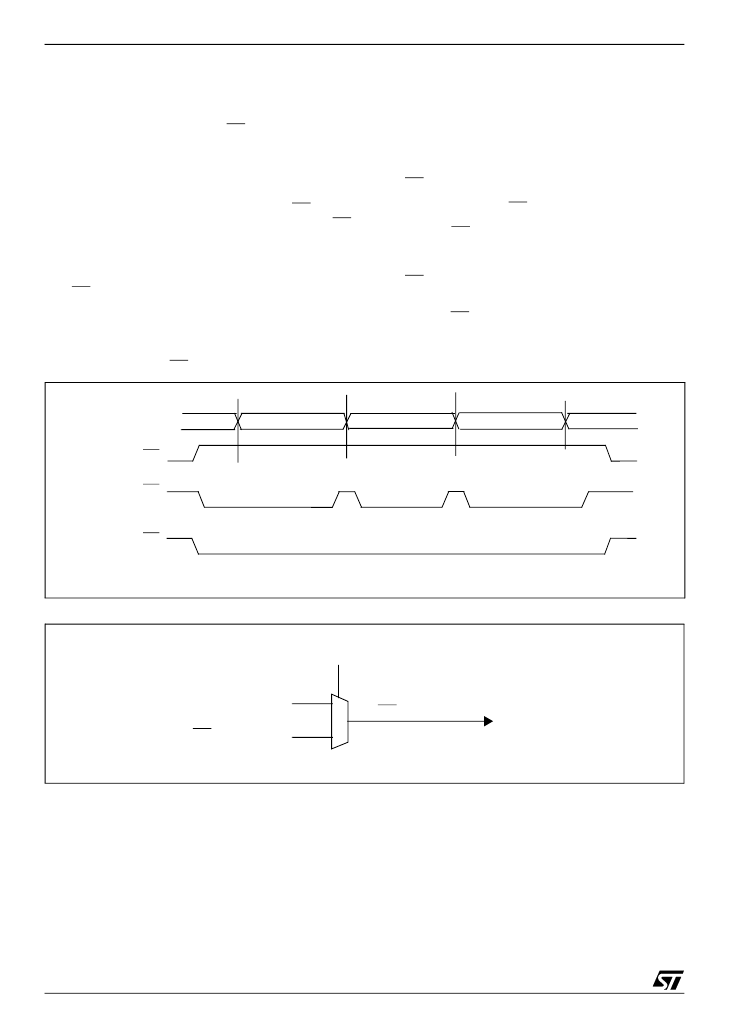

Figure 45. Generic SS Timing Diagram

MOSI/MISO

Master SS

Slave SS

(if CPHA=0)

Slave SS

(if CPHA=1)

Byte 1

Byte 2

Byte 3

Figure 46. Hardware/Software Slave Select Management

SSM bit

SSI bit

SS external pin

1

0

SS internal

76/154

1