ST7232A

SERIAL COMMUNICATIONS INTERFACE

(Cont鈥檇)

10.5.4.7 Parity Control

Parity control (generation of parity bit in transmis-

sion and parity checking in reception) can be ena-

bled by setting the PCE bit in the SCICR1 register.

Depending on the frame length defined by the M

bit, the possible SCI frame formats are as listed in

Table 20.

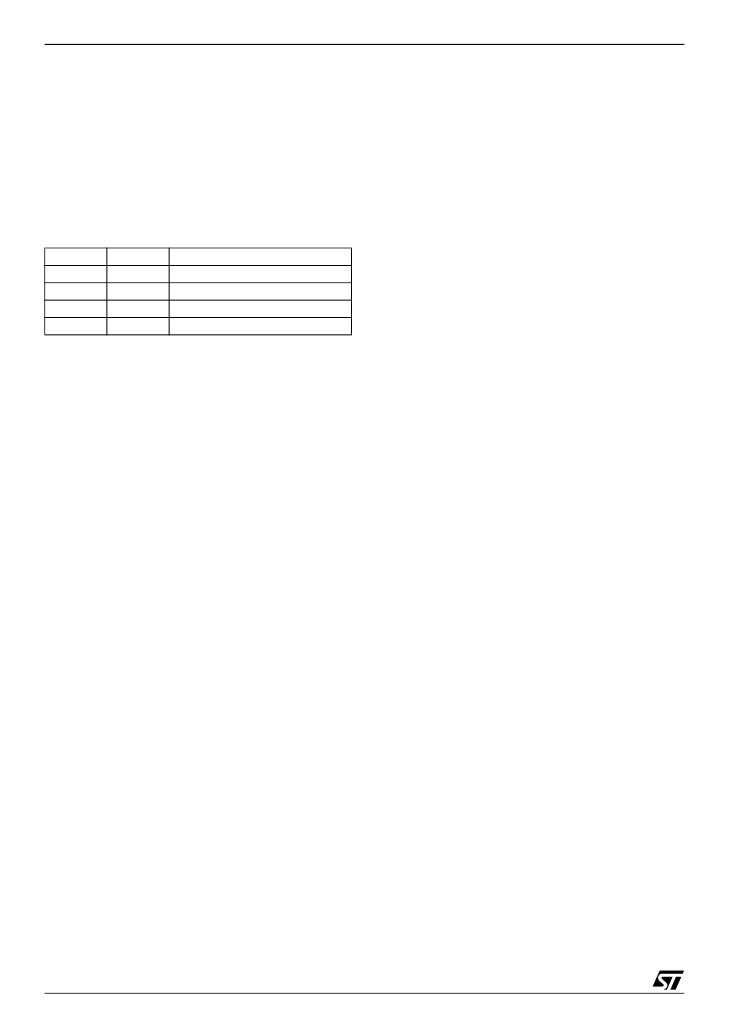

Table 20. Frame Formats

M bit

0

0

1

1

PCE bit

0

1

0

1

SCI frame

| SB | 8 bit data | STB |

| SB | 7-bit data | PB | STB |

| SB | 9-bit data | STB |

| SB | 8-bit data PB | STB |

Legend:

SB = Start Bit, STB = Stop Bit,

PB = Parity Bit

Note:

In case of wake up by an address mark, the

MSB bit of the data is taken into account and not

the parity bit

Even parity:

the parity bit is calculated to obtain

an even number of 鈥?s鈥?inside the frame made of

the 7 or 8 LSB bits (depending on whether M is

equal to 0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be

0 if even parity is selected (PS bit = 0).

Odd parity:

the parity bit is calculated to obtain an

odd number of 鈥?s鈥?inside the frame made of the 7

or 8 LSB bits (depending on whether M is equal to

0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be

1 if odd parity is selected (PS bit = 1).

Transmission mode:

If the PCE bit is set then the

MSB bit of the data written in the data register is

not transmitted but is changed by the parity bit.

Reception mode:

If the PCE bit is set then the in-

terface checks if the received data byte has an

even number of 鈥?s鈥?if even parity is selected

(PS=0) or an odd number of 鈥?s鈥?if odd parity is se-

lected (PS=1). If the parity check fails, the PE flag

is set in the SCISR register and an interrupt is gen-

erated if PIE is set in the SCICR1 register.

10.5.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times.

The majority of the 8th, 9th and 10th samples is

considered as the bit value. For a valid bit detec-

tion, all the three samples should have the same

value otherwise the noise flag (NF) is set. For ex-

ample: if the 8th, 9th and 10th samples are 0, 1

and 1 respectively, then the bit value will be 鈥?鈥?

but the Noise Flag bit is be set because the three

samples values are not the same.

Consequently, the bit length must be long enough

so that the 8th, 9th and 10th samples have the de-

sired bit value. This means the clock frequency

should not vary more than 6/16 (37.5%) within one

bit. The sampling clock is resynchronized at each

start bit, so that when receiving 10 bits (one start

bit, 1 data byte, 1 stop bit), the clock deviation

must not exceed 3.75%.

Note:

The internal sampling clock of the microcon-

troller samples the pin value on every falling edge.

Therefore, the internal sampling clock and the time

the application expects the sampling to take place

may be out of sync. For example: If the baud rate

is 15.625 kbaud (bit length is 64碌s), then the 8th,

9th and 10th samples will be at 28碌s, 32碌s & 36碌s

respectively (the first sample starting ideally at

0碌s). But if the falling edge of the internal clock oc-

curs just before the pin value changes, the sam-

ples would then be out of sync by ~4us. This

means the entire bit length must be at least 40碌s

(36碌s for the 10th sample + 4碌s for synchroniza-

tion with the internal sampling clock).

92/154

1