鈥?/div>

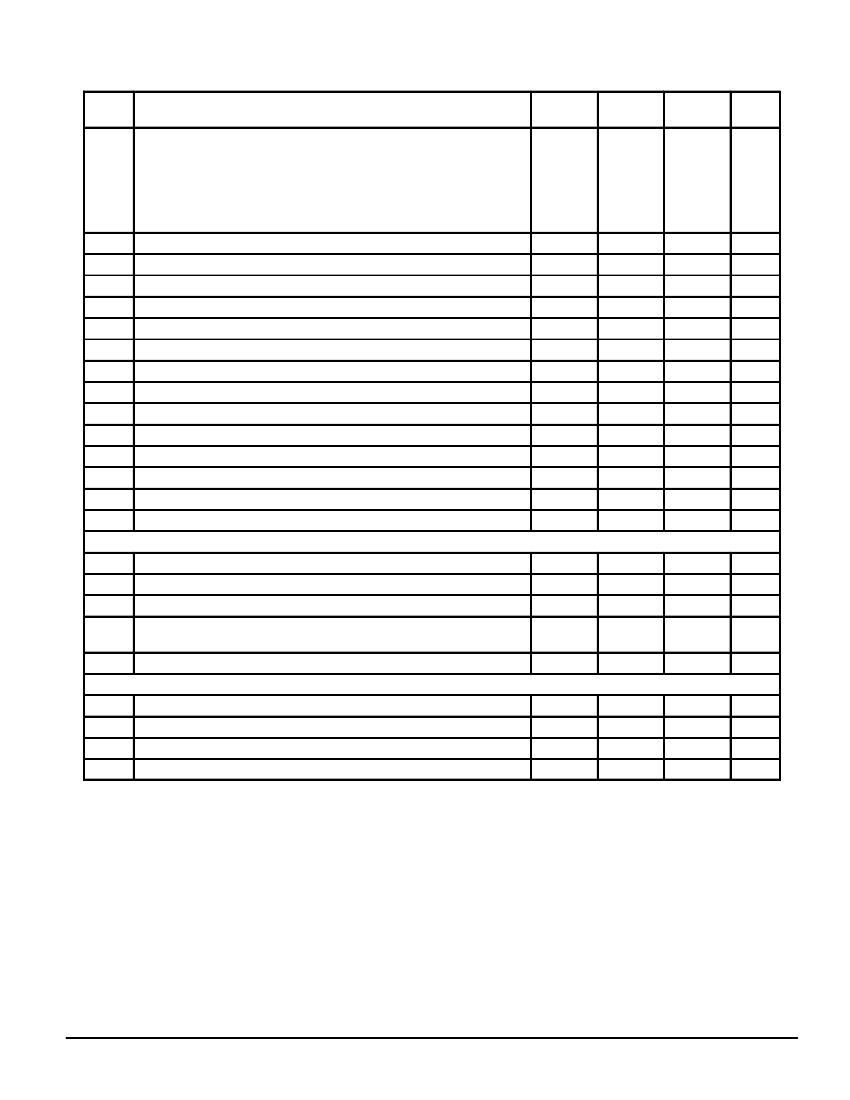

Unit

kHz

1

2

3

4

5

6

7

8

9

10

11

12

13

14

MCLK Duty Cycle for 256 kHz Operation

Minimum Pulse Width High for MCLK (Frequencies of 512 kHz or Greater)

Minimum Pulse Width Low for MCLK (Frequencies of 512 kHz or Greater)

Rise Time for All Digital Signals

Fall Time for All Digital Signals

Setup Time from MCLK Low to FST High

Setup Time from FST High to MCLK Low

Bit Clock Data Rate for BCLKT or BCLKR

Minimum Pulse Width High for BCLKT or BCLKR

Minimum Pulse Width Low for BCLKT or BCLKR

Hold Time from BCLKT (BCLKR) Low to FST (FSR) High

Setup Time for FST (FSR) High to BCLKT (BCLKR) Low

Setup Time from DR Valid to BCLKR Low

Hold Time from BCLKR Low to DR Invalid

%

ns

ns

ns

ns

ns

ns

kHz

ns

ns

ns

ns

ns

ns

MC145481

14

MOTOROLA