Philips Semiconductors

P89LV51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

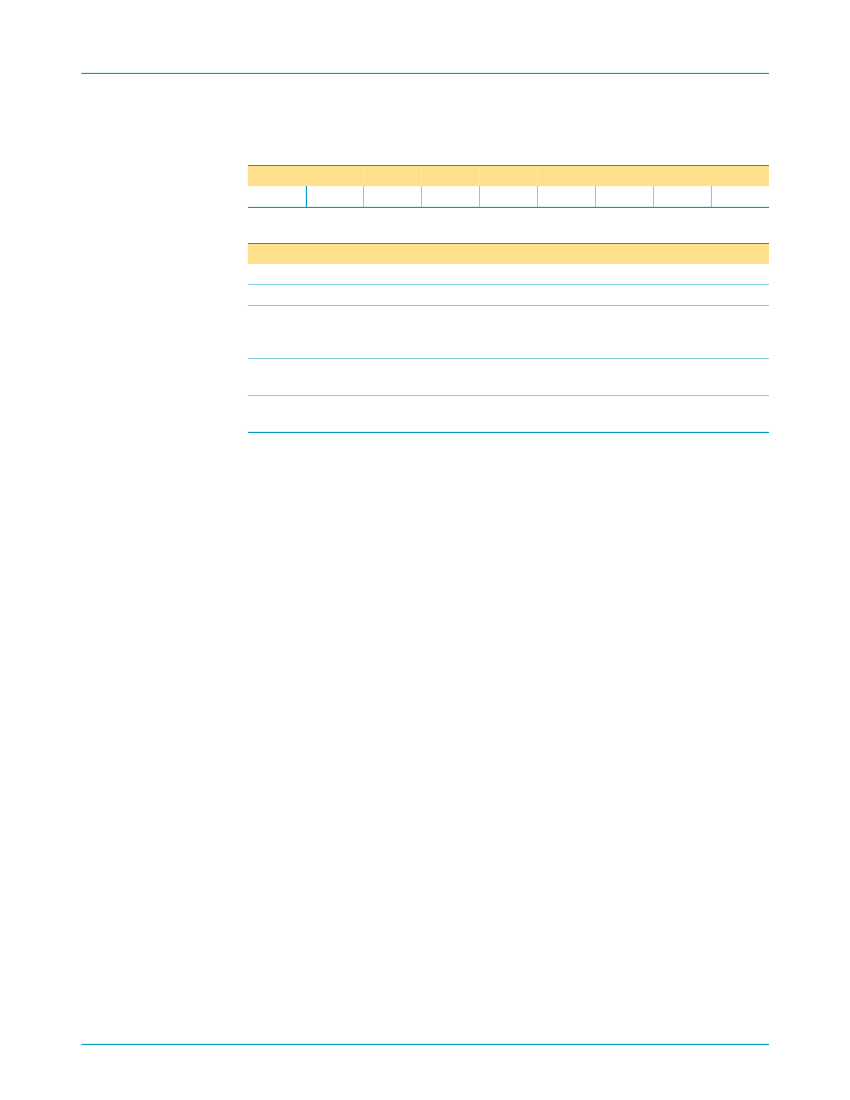

Table 10: AUXR1 - Auxiliary register 1 (address A2H) bit allocation

Not bit addressable; Reset value 00H

Bit

Symbol

Table 11:

Bit

7 to 4

3

2

-

7

-

6

-

5

-

4

3

GF2

0

2

-

1

0

DPS

AUXR1 - Auxiliary register 1 (address A2H) bit description

Symbol

-

GF2

0

Description

Reserved for future use. Should be set to 鈥?鈥?by user programs.

General purpose user-de铿乶ed 铿俛g.

This bit contains a hard-wired 鈥?鈥? Allows toggling of the DPS bit by

incrementing AUXR1, without interfering with other bits in the

register.

Reserved for future use. Should be set to 鈥?鈥?by user programs.

Data pointer select. Chooses one of two Data Pointers for use by

the program. See text for details.

1

0

-

DPS

7.2 Flash memory In-Application Programming

7.2.1

Flash organization

The P89LV51RB2/RC2/RD2 program memory consists of a 16/32/64 kB block. An

In-System Programming (ISP) capability, in a second 8 kB block, is provided to allow

the user code to be programmed in-circuit through the serial port. There are three

methods of erasing or programming of the Flash memory that may be used. First, the

Flash may be programmed or erased in the end-user application by calling low-level

routines through a common entry point (IAP). Second, the on-chip ISP boot loader

may be invoked. This ISP boot loader will, in turn, call low-level routines through the

same common entry point that can be used by the end-user application. Third, the

Flash may be programmed or erased using the parallel method by using a

commercially available EPROM programmer which supports this device.

7.2.2

Boot block (Block 1)

When the microcontroller programs its own Flash memory, all of the low level details

are handled by code that is contained in Block 1. A user program calls the common

entry point in the Block 1 with appropriate parameters to accomplish the desired

operation. Boot block operations include erase user code, program user code,

program security bits, etc.

A Chip-Erase operation can be performed using a commercially available parallel

programmer. This operation will erase the contents of this Boot Block and it will be

necessary for the user to reprogram this Boot Block (Block 1) with the

Philips-provided ISP/IAP code in order to use the ISP or IAP capabilities of this

device. Contact

http://www.semiconductors.philips.com

to obtain the hex 铿乴e for this

device. Questions may be directed to

micro.support@philips.com.

7.2.3

In-System Programming (ISP)

In-System Programming is performed without removing the microcontroller from the

system. The In-System Programming facility consists of a series of internal hardware

resources coupled with internal 铿乺mware to facilitate remote programming of the

9397 750 14342

漏 Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Product data

Rev. 04 鈥?02 December 2004

20 of 77