PIC18F2455/2550/4455/4550

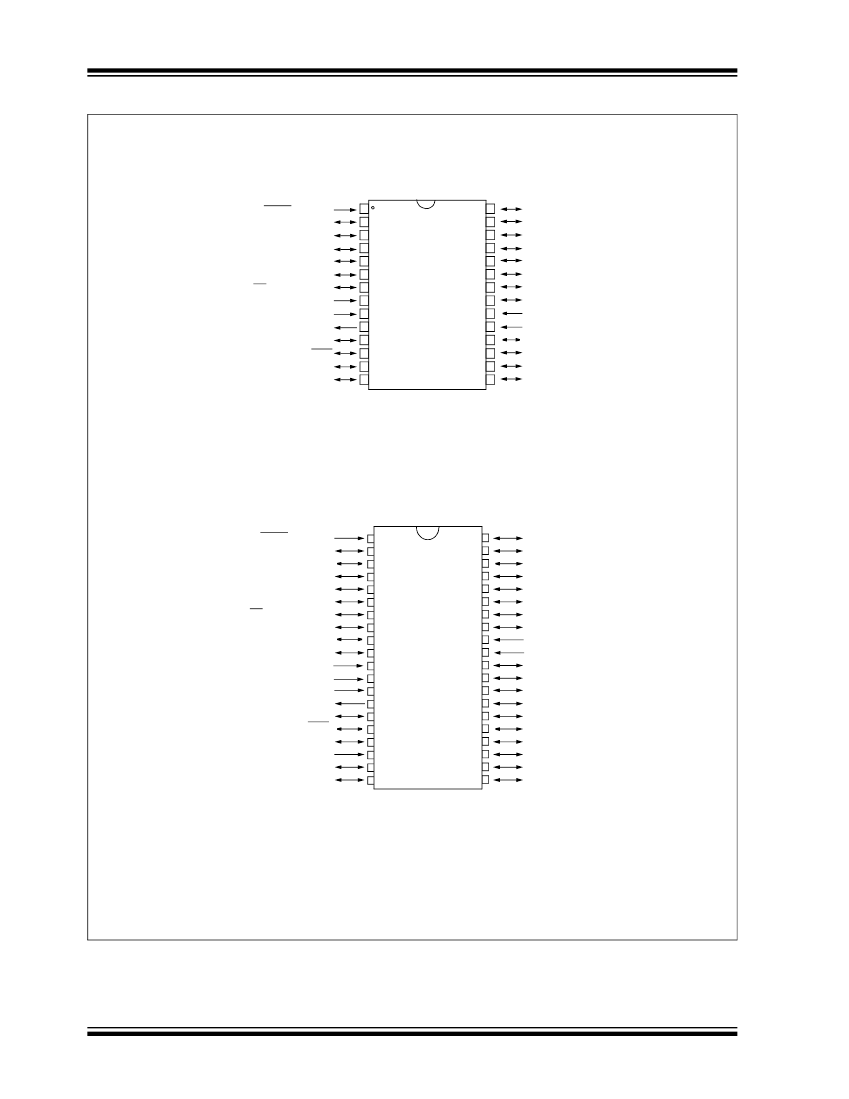

Pin Diagrams

28-Pin SDIP, SOIC

MCLR/V

PP

/RE3

RA0/AN0

RA1/AN1

RA2/AN2/V

REF

-/CV

REF

RA3/AN3/V

REF

+

RA4/T0CKI/C1OUT

RA5/AN4/SS/LVDIN/C2OUT

V

SS

OSC1/CLKI/RA7

OSC2/CLKO/RA6

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2*/UOE

RC2/CCP1

V

USB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/AN11/KBI0/RCV

RB3/AN9/CCP2*/VPO

RB2/AN8/INT2/VMO

RB1/AN10/INT1/SCK/SCL

RB0/AN12/INT0/SDI/SDA

V

DD

V

SS

RC7/RX/DT/SDO

RC6/TX/CK

D+/VP

D-/VM

PIC18F2455

40-Pin PDIP

MCLR/V

PP

/RE3

RA0/AN0

RA1/AN1

RA2/AN2/V

REF

-/C

VREF

RA3/AN3/V

REF

+

RA4/T0CKI/C1OUT

RA5/AN4/SS/LVDIN/C2OUT

RE0/CK1SPP/AN5

RE1/CK2SPP/AN6

RE2/OESPP/AN7

AV

DD

AV

SS

OSC1/CLKI/RA7

OSC2/CLKO/RA6

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2*/UOE

RC2/CCP1/P1A

V

USB

RD0/SPP0

RD1/SPP1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/AN11/KBI0/CSSPP

RB3/AN9/CCP2*/VPO

RB2/AN8/INT2/VMO

RB1/AN10/INT1/SCK/SCL

RB0/AN12/INT0/SDI/SDA

V

DD

V

SS

RD7/SPP7/P1D

RD6/SPP6/P1C

RD5/SPP5/P1B

RD4/SPP4

RC7/RX/DT/SDO

RC6/TX/CK

D+/VP

D-/VM

RD3/SPP3

RD2/SPP2

PIC18F4455

Note:

*

Pinouts are subject to change.

Assignment of this feature is dependent on device configuration.

DS39617A-page 2

Advance Information

PIC18F4550

PIC18F2550

铮?/div>

2003 Microchip Technology Inc.