Philips Semiconductors

Product speci铿乧ation

Dual smart card interface

If a start bit is detected on the I/O during the first 200 CLK

pulses, then it is omitted. If a start bit is detected between

200 and 352 CLK pulses, then bit EARLY is set in the

status register. If the card starts answering before

41950 CLK pulses, then RST remains LOW level. If not,

after 41950 CLK pulses, RST is toggled HIGH. If, again, a

start bit is detected within 352 CLK pulses, bit EARLY is

set in the status register. If the card does not answer

before 41950 new CLK pulses, then bit MUTE is set in the

status register. If the card answers within the correct

window, then the CLK count is stopped and the system

controller may send commands to the card.

Deactivation is initiated either by the system controller

(reset bit START), or automatically in the event of a

hardware problem or supply drop-out. With a supply

drop-out both cards are deactivated at the same time.

During deactivation, RST goes LOW, the clock is stopped

and the I/O lines go LOW. V

CC

then goes low with a

controlled slope and the DC/DC converter is stopped if no

card is active.

Outside a session, cards contacts are forced low

impedance to CGND.

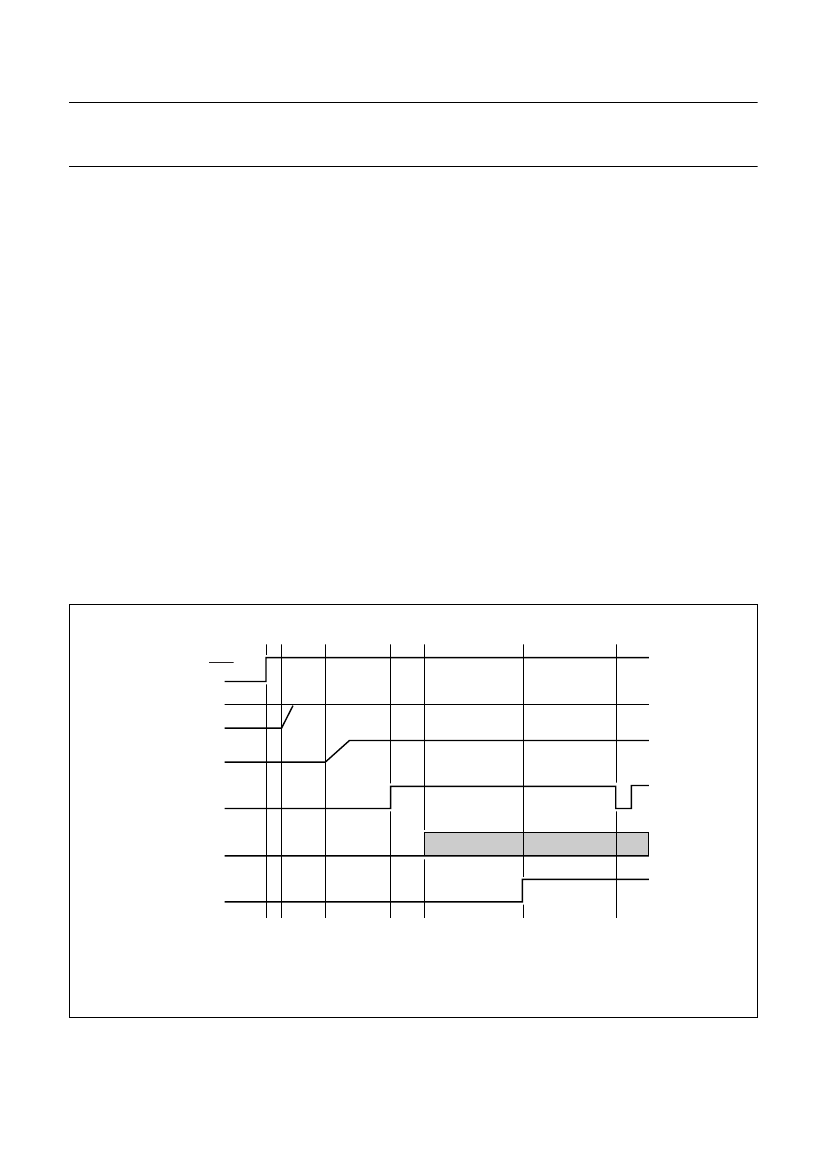

Activation sequence

TDA8020HL

When the cards are inactive, V

CC

, CLK, RST and I/O are

LOW, with low impedance with respect to CGND. The

DC/DC converter is stopped.

When everything is satisfactory (voltage supply, card

present and no hardware problems), the system controller

may initiate an activation sequence of a present card

(see Fig.4):

鈥?/div>

The DC/DC converter is started (t1). If one card was

already active, then the DC/DC converter was already

on, and nothing more occurs at this step

鈥?/div>

V

CC

starts rising from 0 to 5 or 3 V with a controlled rise

time of 0.14 V/碌s typical (t2)

鈥?/div>

I/O rises to V

CC

(t3); internal 10 k鈩?pull-up resistors to

V

CC

鈥?/div>

CLK is sent to the card and RST is enabled (t4 = t

act

).

If the card does not answer within the first 41950 CLK

cycles, then RST is raised HIGH (t5).

The sequencer is clocked by f

int

/64 which leads to a time

interval T of 25

碌s

typical. Thus t1 = 0 to T/64;

t2 = t1 + 3T/2; t3 = t1 + 7T/2 and t4 = t1 + 4T.

handbook, full pagewidth

START/STOP

VUP

VCC

I/O

CLK

RST

t0 t1

t2

t3

t4

t5

ATR

FCE837

t4 = t

act

.

Fig.4 Activation sequence.

2001 Aug 15

10