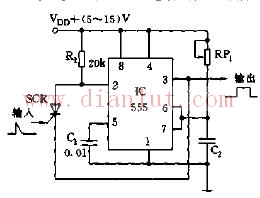

基于555集成芯片构成可控硅控制的触发器电路

出处:xwj 发布于:2011-08-27 21:31:01 | 3093 次阅读

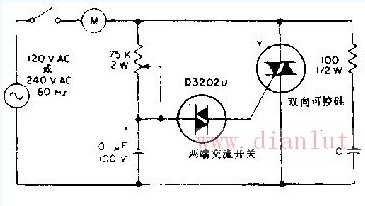

如图所示,555和R1、RP1、C2等组成触发延时电路。平时,由于R1接VDD,使555处于复位状态,即3脚呈低电平;当触发信号到来时,SCR导通,2脚有一低电平信号,使555翻转置位,输出高电平,暂稳宽度为τ=1.1RP1C2。触发后,SCR关断。这种电路可降低对触发脉冲的要求。若用CMOS型555(或556),还可减小触发电流。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。