实现高分辨率(16 位)DAC 的最高 8 位解决 PWM 迟钝问题

出处:维库电子市场网 发布于:2024-08-22 16:12:29 | 546 次阅读

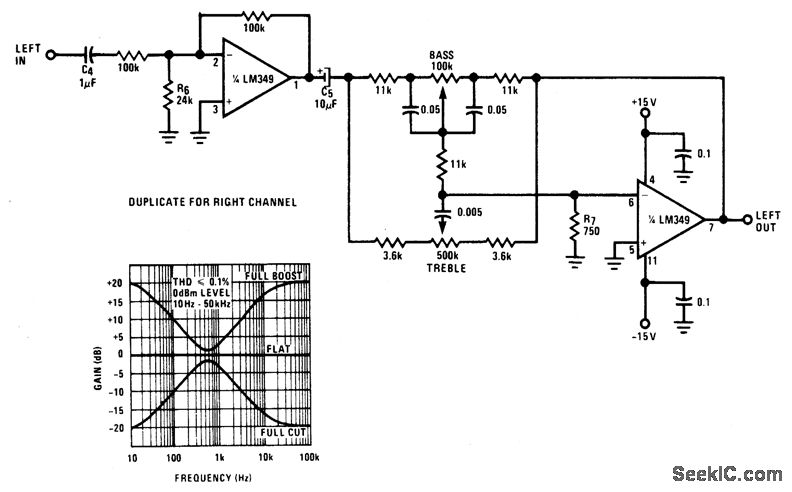

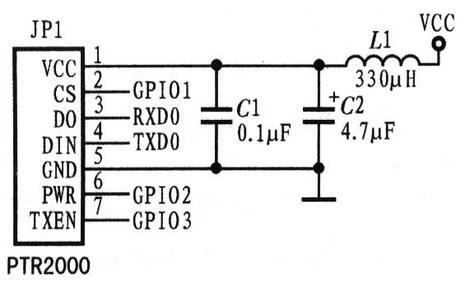

图 1提供了一种解决 PWM 迟钝问题的方案,即使用它来实现高分辨率(16 位)DAC 的最高 8 位,而另一种技术(数字电位器)提供低 8 位。然后,两个输出在一个简单的 256:1 比例电阻分压器中被动相加。这样做的好处是稳定速度提高了 256 倍(与使用 PWM 进行完整的 16 位计数相比),同时还具有 16 位分辨率、单调性、线性度(INL 和 DNL)和微伏零点稳定性。该电路仅靠从单个 5V 电源轨吸取的几 mA 电流运行,同时还集成了相当不错的电压基准。

有源低通模拟纹波减法滤波通过R1C1 + R2C2 网络进行,如“使用模拟减法消除 PWM DAC 纹波”中所述。如果我们假设256/32 MHz = 8 ?s PWM 周期,则所示的4.99 kΩ x 0.1 ?F = 499 ?s RC 时间常数适用于 16 位 (96 dB) 纹波衰减。电容当然需要根据不同的 PWM 时钟频率进行比例调整。

同时,1k Dpot U2 提供 SPI 控制、8 位分辨率、0 至 2.5v lsbyte 贡献,该贡献通过 R2R3 分压器以 256:1 的比例与 U1 的 PWM 输出相加。R2:R3 比率应准确且稳定,优于 0.5%。R3 远高于电位器提供的 2.5k(最大)可变阻抗,因此其对非线性的贡献保持小于 +/-? lsb。

上一篇:使用电流镜控制电源

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。