电压控制电路中 FET 的使用指南,第 5 部分

出处:维库电子市场网 发布于:2024-09-19 17:17:02 | 677 次阅读

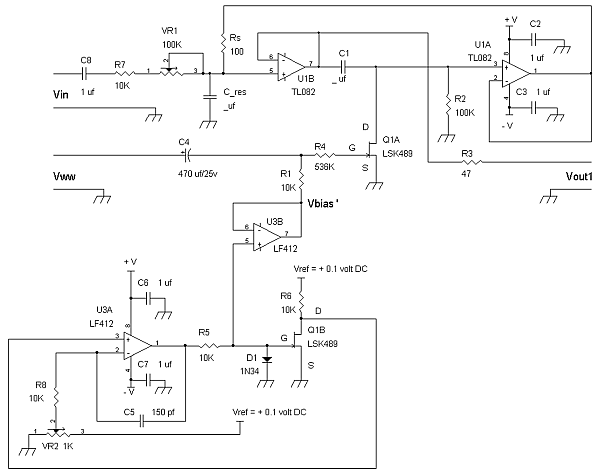

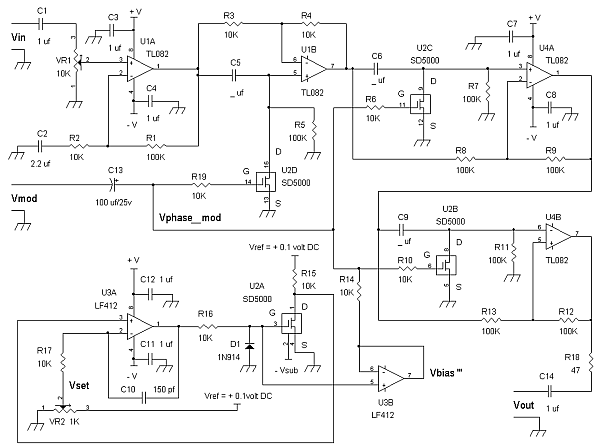

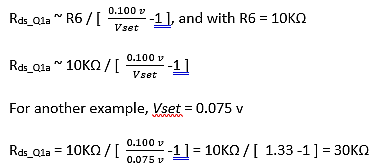

通过使用具有小直流偏置电压 Vref = +100 mV DC 和已知负载电阻 R6 的参考 FET Q1B,我们可以通过电位器 VR2 引脚 2 将电压设置为 R8,将 Q1B 偏置到任何漏极到源极电阻 R ds。 小直流电压 Vref 设置为 +100 mV DC,以确保 Q1B 仍处于三极管或欧姆区域。如果我们将 VR2 的滑块电压设置为 Vset 以提供一半电压或 +50 mV,这将导致偏置伺服电路打开 Q1B,直到其漏极电压也为 +50 mV DC。如果我们通过 10KΩ 串联电阻 R6 在 Q1B 的漏极获得 +100 mV 的一半 = 50 mV,这意味着漏极到源极电阻也是 10KΩ。因为偏置伺服电路是一个负反馈电路,无论我们在 VR2 的滑块上设置什么电压,该滑块都会耦合到 U3A 的 (-) 输入,所以其 (+) 输入必须通过输入端子之间的虚拟短路跟随该电压。由于 (+) 输入端子连接到 Q1B 的漏极,因此其漏极电压必须与 VR2 滑块上的电压相匹配。补偿电容器 C5 可确保电路不会振荡。为了更好地抑制噪声,C5 可以高达 1 uf。 当 Vset = VR2 引脚 2 处的电压时,求解 Q1A 的 R ds的一般方程 为:

注意:二极管 D1 确保参考 FET 的栅极在开启期间不会正向偏置。如果栅极正向偏置,偏置伺服电路可能会“卡住”。

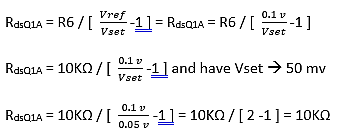

就低失真而言,最大输入信号幅度通常为峰峰值 150 mV。 现在让我们看一下图 41,哇音电压控制带通滤波器通过 Rfb 和 R4 带有偏置伺服电路的降低失真反馈。

由于降低失真的反馈网络 Rfb 和 R4 对栅极的衰减约为 50%,因此放大器 U3B 的增益设置为 2 以补偿这一点。请注意,R1

尽管增加 Q1B 的栅极电压可使 Q1A 的 R ds接近相同 ,但对于 Q1A 和 Q1B 相同的栅极电压,Q1A 的漏极至源极电阻实际上更低。原因是电阻网络 Rfb 和 R4 形成负反馈效应,略微降低了 Q1A 的 R ds。也就是说 R dsQ1A dsQ1B 略有降低。

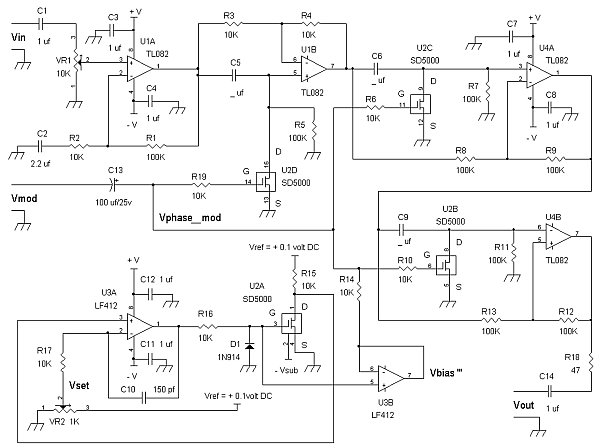

尽管如此, 与手动操作相比,图 41仍然提供了一种更简单的偏置 FET 的方法。稍后我们将重新讨论图 41的更准确方法 。 现在,让我们看一下图 42中的相移系统的偏置伺服电路。它使用与图 40相同的偏置伺服电路,但这次使用 MOSFET 作为压控电阻。请注意,D1 反向连接,以确保开启时栅极到源极电压不会对 N 通道增强器件产生过负的影响。

该电路的总相移为:

例如,Vset = 0.033 v = 引脚 2 VR2 处的电压,则

请注意,–Vsub = ?5 伏至 ?10 伏直流电,以确保基板偏置正确。

可以使用一个 1000 uf 电解电容器(其 (+) 端子位于 VR2 的引脚 2)将调制信号耦合到 VR2 引脚 2,而不是使用 Vww。 参见图 43,改进的伺服偏置电路。

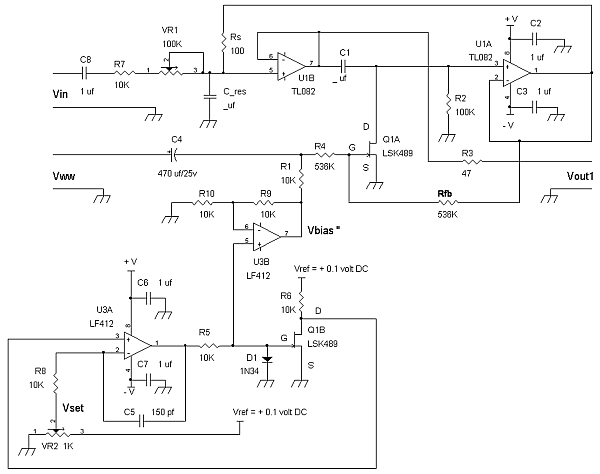

为了更准确地确定 Q1A 的 R ds ,偏置伺服电路通过 U4A 复制反馈网络,U4A“复制”U1A,R10 和 R9 复制 Rfb 和 R4。

我们还应注意,尽管该电路可以更精确地设置正确的栅极偏置电压,但由于 Rfb 和 R4 的负反馈效应,Q1A 的实际漏极至源极电阻会略低。因此,我们将使用“~”代替“=”表示近似值 偏置由 VR2 引脚 2 处的滑块电压 Vset 设置,使得:

注意: 通过将 FET 的漏极到源极电阻设置为更高的值,可以实现更低的失真。例如,我们将 R6 设置为 51KΩ 而不是 10KΩ,并将 R ds_Q1a 设置为 > 100KΩ 范围。

对于图 41 和 43中的 P 通道 JFET 器件,请使用负 Vref(例如 – 100 mV DC)和反向二极管 D1 的连接。对于图 42中的 P 通道 MOSFET ,请使用负 Vref(例如 – 100 mV DC)和反向二极管 D1 的连接。

最后的建议和想法

DMOS 器件具有漏极至栅极电容非常低的优势。要使用双列直插式封装 (DIP) 中的这些器件(例如 SD5000 系列),请确保通过电阻(例如 1KΩ 至 10KΩ)偏置衬底引脚,电压源的电压应比任何其他引脚上出现的电压更负或更低。例如,如果最小源电压为地,则衬底电压应为 ?2 伏至 ?9 伏。如果漏极和源极之间的交流信号很小,例如

有些 DMOS FET 的栅极电容非常低,并且没有内部齐纳二极管的保护,否则会增加更多的栅极电容。DMOS 器件(如 SD211 和 SD214)带有短接导线。首先将栅极和源极引线焊接到提供从栅极到源极的直流路径的电路上,然后可以移除短接导线。在短接导线完好无损的情况下,您可以在移除短接导线之前(但在将 DMOS FET 焊接到电路之前)在栅极和源极引线上焊接一个 10KΩ 电阻。

本文介绍了一些基本的电压控制电路。这些电路可用于更复杂的系统,例如吉他效果踏板。例如,图 8 至 15中所示的带反馈的电压控制电阻电路也可以通过过驱动输入信号用作对称削波电路。没有反馈的电压控制衰减器电路(例如,通过移除图 8 至 15中的 R3 )可以通过再次过驱动输入信号用作非对称削波器。这些削波电路可以并入电吉他模糊踏板中。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。