JFET 共源共栅提高了电流源性能

出处:维库电子市场网 发布于:2024-10-12 16:21:37 | 427 次阅读

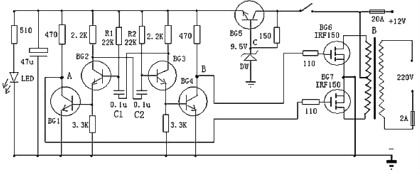

当栅源偏置电压为 0V 时,N 沟道 JFET 在最大饱和漏极电流下作为耗尽型器件运行。与需要栅极偏置电压才能导通的耗尽型 MOSFET 不同,JFET 在默认导通状态下工作,需要栅极偏置电压来切断导通。当其栅源电压相对于源极变得更负时,JFET 的漏极电流在夹断电压处变为零。 JFET 的漏极电流大致随其栅极偏压变化: I D ≈I DSS ×(1+V GS /V P ) 2,其中 I D 为漏极电流,I DSS 为饱和漏极电流,V GS 为栅极至栅极电压。 -源电压,V P 是夹断电压。

假设IC 1的输出电压V REF保持恒定在1.8V。由于输出电压驱动Q 2的栅极,因此IC 1的输入电压V IN等于V REF –V GS(Q2),即1.8V–(–1.2V)=3V。因此,Q 2的栅源电压保持在其1.2V的标称夹断电压,并且随着电流源的微小变化而同步变化。当电源电压从 3V 变化到 30V 以上时,输入电压几乎保持恒定,正如您所期望的,因为 V REF 也保持恒定。共源共栅 FET 配置使电流源的诺顿等效电阻超过了电压基准和单独的 R 1 的电阻 。您可以使用单个 JFET,但堆叠两个 JFET 可以进一步增强电路的有效阻抗。请注意,IC 1 不会降低精度,因为 JFET 使 IC 1的输入电压几乎保持恒定,并且 IC 1 有效地消除了初始栅源电压变化以及 Q 1 和 Q 2 引入的温度效应。

由V IN、V REF和V GS(Q2)组成的基尔霍夫电压环路中的负反馈允许漏极电流达到满足Q 2传输方程的 平衡偏置点。 Q 2的漏极电流由 (V REF /R 1 ) 加上 IC 1的内部“内务”电流 I GND之和组成,保持恒定。添加 Q 1可以将 Q 2输出阻抗 的影响降低到微不足道的程度。调整 R 1的值 可在 200 ?A 至 5 mA 的有用范围内改变电路的输出电流,其中 Q 2的饱和漏极电流规格规定了上限。如果您选择具有较高饱和漏极电流的 JFET,请确保不超过 Q 1的最大功耗。

请注意,电路的电源电压下限必须超过电路的顺从电压 3V 加上传感器引入的压降:I SOURCE ×R 2。电路的电源电压上限不得超过I SOURCE ×R 2 +30V。例如,向 1kΩ 压力传感器桥 R 2提供 2.5mA 的电流,将电源电压范围限制为 5.5 至 32.5V。该电路的输出电流在很宽的电源电压范围内变化小于 1 ?A(图 2 )。

上一篇:电磁阀保护电路

下一篇:运算放大器线性化衰减器控制响应

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。