高速脉冲发生器具有可编程级别

出处:维库电子市场网 发布于:2024-10-16 16:53:42 | 395 次阅读

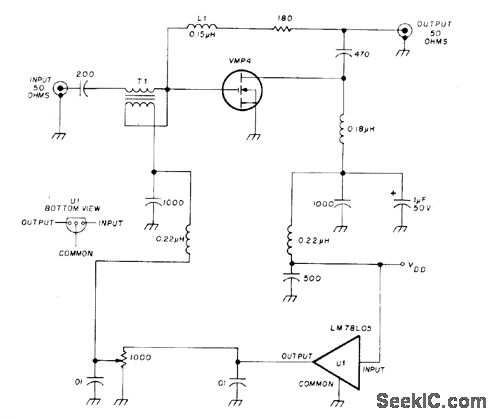

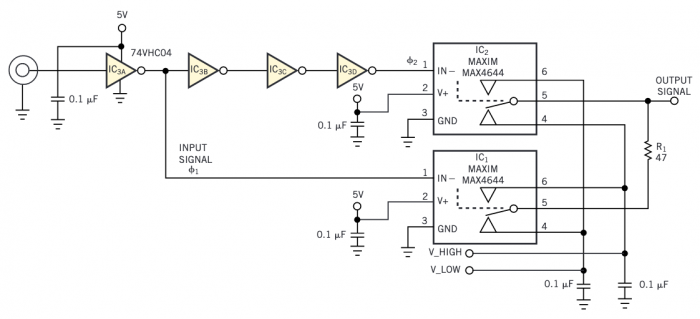

设计人员也将高速数字电路使用的亚微米工艺应用于模拟开关,因此这些开关的开启和关闭时间也会产生快速的上升和下降时间。此外,SPDT(单刀双掷)开关可以产生高电平和低电平可编程的脉冲。 模拟开关阻碍其用作脉冲发生器的一个特性是固有的内置延迟(先断后合时间),该延迟可保证 SPDT 开关在转换期间不会将两个开关端子短路在一起。不幸的是,这种延迟和开关的有限开启时间也延长了上升和下降时间。您可以通过向电路添加动态上拉和动态下拉来避免这种影响(图 1)。足够低的上拉和下拉阻抗可以极大地改善相应的上升和下降时间。

考虑稳态条件,其中 F 1较低且 F 2高。 IC 1的COM 引脚和IC 2的COM 引脚连接到V_LOW,F 1的上升沿导致IC 1将输出信号拉高。由于串联电阻R 1相对于MAX4644的导通电阻较大,即47W与2.5W典型值相比,因此对输出电压的直接影响很小。然而,当 F 1传播通过反相器串时,F 2的下降沿导致 IC 2从 V_LOW 转变为 V_HIGH。低阻抗上拉电阻 R 1的存在为信号转换提供驱动,随后 IC 2很快闭合。

C55输入信号为 5V 逻辑,输出摆幅为 1 至 2V(图 2)。您可以将 V_LOW 和 V_HIGH 设置为 IC 1和 IC 2电源范围内的任意电平。该电路的静态电流基本上为零,仅在输出转换期间出现短暂的峰值。输出的上升和下降时间约为 4 纳秒,输出阻抗为 2.5W。

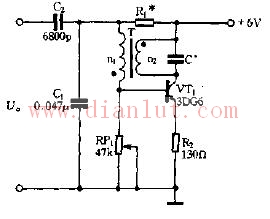

上一篇:阿姆斯壮振荡器设计

下一篇:陷波滤波器对元件公差不敏感

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。