PMOS 开关电路常见问题全解析及有效排查策略

出处:网络整理 发布于:2025-04-28 10:58:05 | 597 次阅读

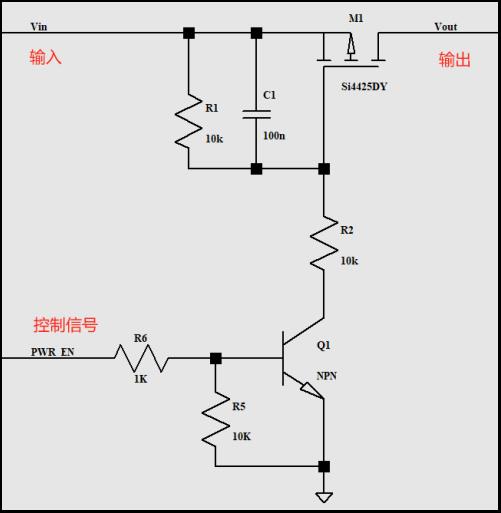

PMOS 开关电路基本原理

为了更好地理解后续的问题及解决方法,我们先来了解一下 PMOS 开关电路的基本工作原理以及各个器件的作用。当控制信号 PWR_EN 为高电平时,三极管 Q1 导通,R2 下端接地。由于 R1 和 R2 的分压作用,MOS 管 M1 的 Vgs 会产生压差 Vgs = -Vin * R1 / (R1 + R2),从而使 M1 导通。相反,当控制信号 PWR_EN 为低电平时,三极管 Q1 不导通,R2 下端悬空,MOS 管 M1 的栅极会被 R1 拉到与输入电压 Vin 相同,即 Vgs = 0,M1 处于不导通状态。通过控制 PWR_EN 的高低,我们就能实现对 PMOS M1 导通和关断的控制,这就是该电路的基本原理。

PMOS 开关电路常见问题及解决办法

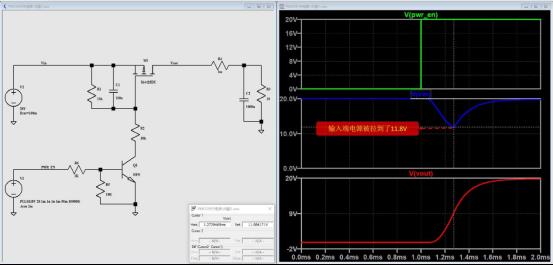

通过改变内阻和负载电容进行仿真实验,我们发现内阻越大、负载端电容量越大,电压跌落越明显。若负载需要大电容,我们可以通过调整 R1、R2、C1 的大小来调整 PMOS 开关开通时间,增大开关开通时间 t,从而降低充电电流,减小电源跌落。例如,保持电源内阻为 100mΩ,滤波电容为 1000uF 不变,调整 gs 之间的跨接电容或 R1、R2 的值,都能观察到电压跌落的变化。

需要注意的是,实际电路比仿真更为复杂,除了内阻,还存在电感等因素,同时输入端的电容在开通瞬间也会给负载电容提供电流,可能使最终跌落不明显。此外,输入源端可能有限流保护,开通瞬间拉取电流过大可能导致前级过流保护,使电源被拉死,这些都需要具体情况具体分析。

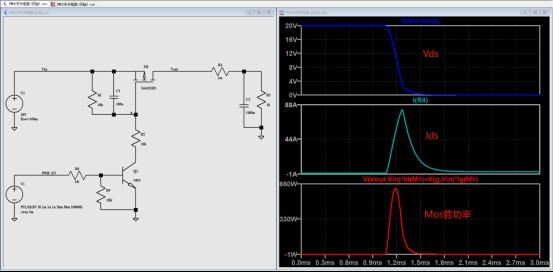

我们可以通过调节外围电阻或电容,让 PMOS 更慢开通,从而降低电流。例如,将 gs 间跨接电容分别调至 470nF、1uF、4.7uF,当 Cgs = 1uF 时,Ids 最大只有 40A,满足 80% 的降额要求。同时,我们还需要结合 SOA 曲线判断功率是否超标。假设该 PMOS 应用场景为单脉冲,通过计算可知,调整 Cgs 电容到 1uF 后,实际功率未超过 PMOS 的功率限制,能工作在 SOA 区,避免损坏。在实际电路应用中,我们一般需要测量 PMOS 开通时的电压和电流曲线,以此判断是否安全。

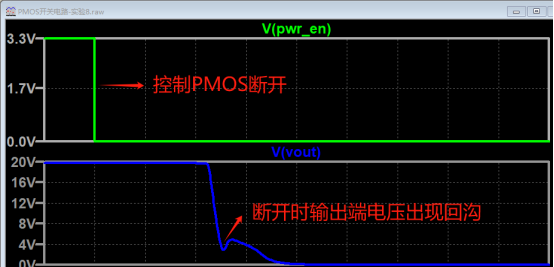

通过仿真波形可以发现,回沟出现的时刻正是 PMOS 的 Vgs 电压等于其 Vgsth 的时候。为了解决回沟问题,我们可以让 PMOS 更快关闭,例如将 PMOS 的 g 和 s 跨接的电容从 100nF 调整到 10nF,回沟基本消失。此外,在输出端加一个滤波电容也能避免负载等效 RL 突然变大。加滤波电容后,等效负载变为原本的 RL 和新加电容阻抗的并联,即使原本的 RL 突然变大,总的负载阻抗也不会变得很大。仿真结果显示,在负载端加一个 1uF 的滤波电容后,Vout 完全没有回沟,下电波形良好。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。