鈥?/div>

Empty and Almost-Full flags

Separate SCLK input for Serial programming of flag offsets

User selectable input and output port bus-sizing

- x9 in to x9 out

- x9 in to x18 out

- x18 in to x9 out

- x18 in to x18 out

Big-Endian/Little-Endian user selectable byte representation

Auto power down minimizes standby power consumption

Master Reset clears entire FIFO

Partial Reset clears data, but retains programmable settings

Empty, Full and Half-Full flags signal FIFO status

Select IDT Standard timing (using

EF

and

FF

flags) or First Word

Fall Through timing (using

OR

and

IR

flags)

Output enable puts data outputs into high impedance state

JTAG port, provided for Boundary Scan function

Available in 144-pin (13mm x 13mm) or 240-pin (19mm x 19mm)

PlasticBall Grid Array (PBGA)

Easily expandable in depth and width

Independent Read and Write Clocks (permit reading and writing

simultaneously)

High-performance submicron CMOS technology

Industrial temperature range (鈥?0掳C to +85掳C) is available

掳

掳

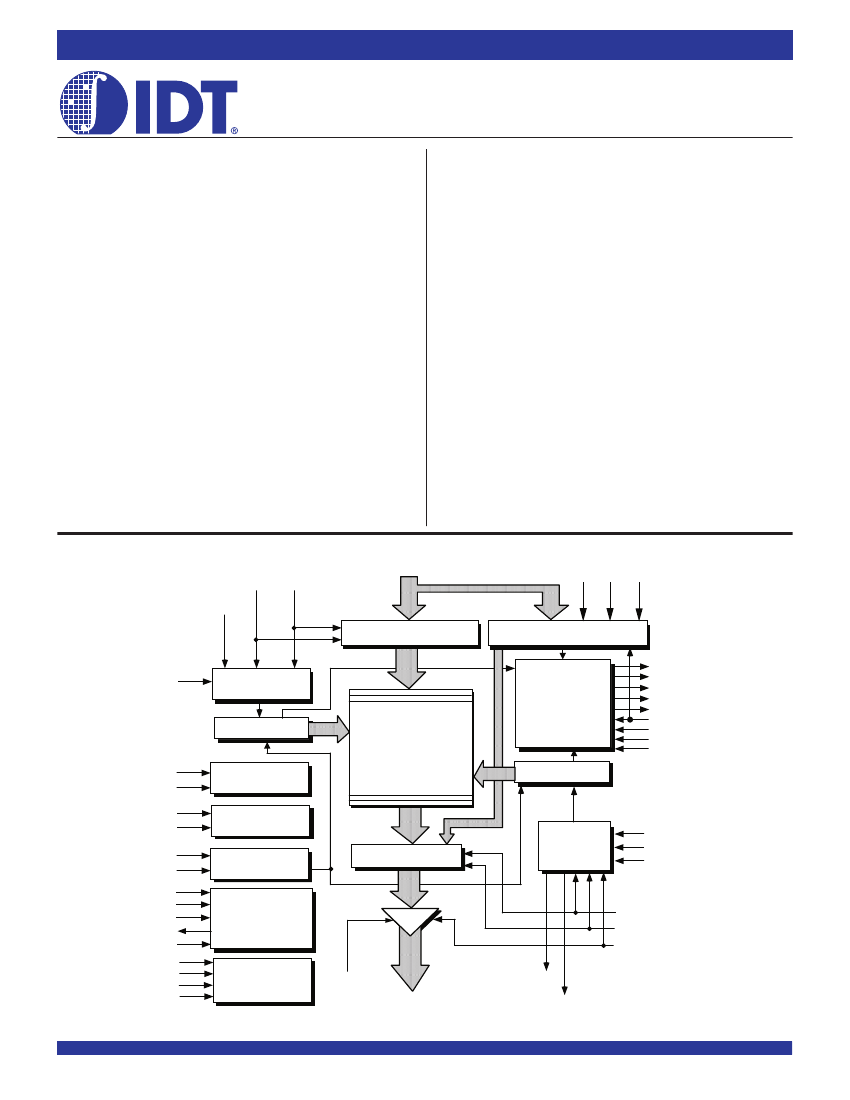

FUNCTIONAL BLOCK DIAGRAM

D

0

-D

n

(x18 or x9)

WEN

WCLK/WR

WCS

LD

SEN

SCLK

INPUT REGISTER

OFFSET REGISTER

FF/IR

PAF

EF/OR

PAE

HF

FWFT/SI

PFM

FSEL0

FSEL1

ASYW

WRITE CONTROL

LOGIC

RAM ARRAY

2,048 x 18 or 4,096 x 9

4,096 x 18 or 8,192 x 9

8,192 x 18 or 16,384 x 9

16,384 x 18 or 32,768 x 9

32,768 x 18 or 65,536 x 9

65,536 x 18 or 131,072 x 9

131,072 x 18 or 262,144 x 9

262,144 x 18 or 524,288 x 9

524,288 x 18 or 1,048,576 x 9

FLAG

LOGIC

WRITE POINTER

BE

IP

IW

OW

MRS

PRS

TCK

TRST

TMS

TDO

TDI

Vref

WHSTL

RHSTL

SHSTL

CONTROL

LOGIC

BUS

CONFIGURATION

RESET

LOGIC

READ POINTER

OUTPUT REGISTER

READ

CONTROL

LOGIC

RT

MARK

ASYR

JTAG CONTROL

(BOUNDARY SCAN)

RCLK/RD

REN

RCS

HSTL I/0

CONTROL

OE

EREN

5909 drw01

Q

0

-Q

n

(x18 or x9)

ERCLK

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. TeraSync FIFO is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

1

铮?/div>

2003 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

SEPTEMBER 2003

DSC-5909/16