ST72260G, ST72262G, ST72264G

INTERRUPTS

(Cont鈥檇)

Servicing Pending Interrupts

As several interrupts can be pending at the same

time, the interrupt to be taken into account is deter-

mined by the following two-step process:

鈥?the highest software priority interrupt is serviced,

鈥?if several interrupts have the same software pri-

ority then the interrupt with the highest hardware

priority is serviced first.

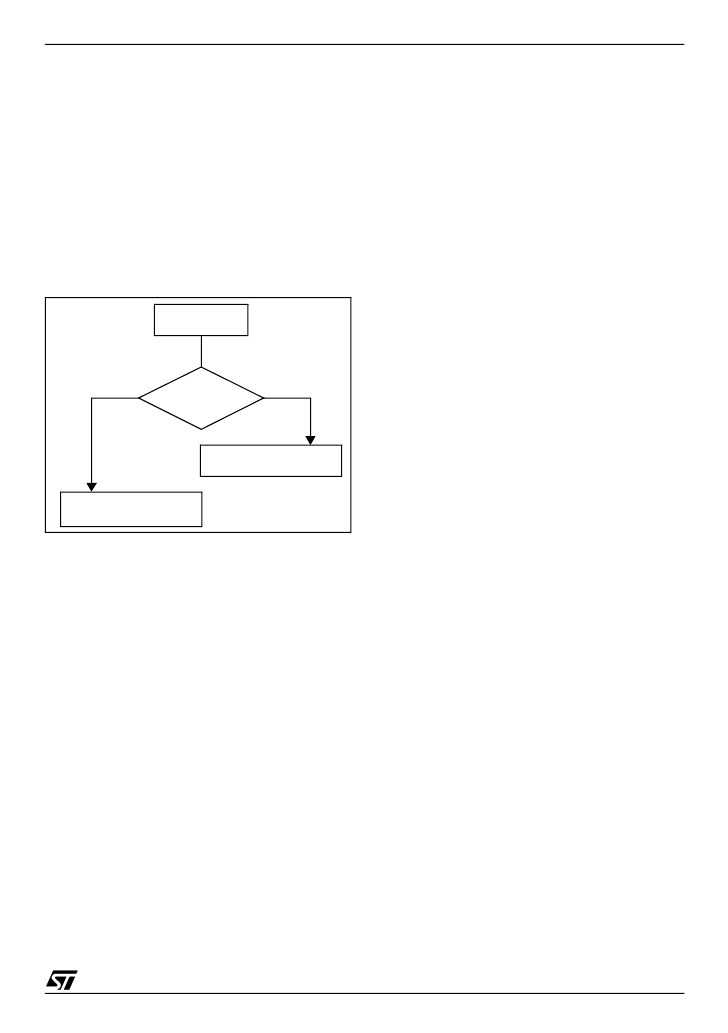

Figure 18

describes this decision process.

Figure 18. Priority Decision Process

PENDING

INTERRUPTS

3). These sources allow the processor to exit

HALT mode.

s

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP

instruction is executed. It will be serviced accord-

ing to the flowchart on

Figure 17

as a TLI.

s

RESET

The RESET source has the highest priority in the

ST7. This means that the first current routine has

the highest software priority (level 3) and the high-

est hardware priority.

See the RESET chapter for more details.

Maskable Sources

Maskable interrupt vector sources can be serviced

if the corresponding interrupt is enabled and if its

own interrupt software priority (in ISPRx registers)

is higher than the one currently being serviced (I1

and I0 in CC register). If any of these two condi-

tions is false, the interrupt is latched and thus re-

mains pending.

s

External Interrupts

External interrupts allow the processor to exit from

HALT low power mode.

External interrupt sensitivity is software selectable

through the Miscellaneous registers (MISCRx).

External interrupt triggered on edge will be latched

and the interrupt request automatically cleared

upon entering the interrupt service routine.

If several input pins of a group connected to the

same interrupt vector request an interrupt simulta-

neously, the interrupt vector will be serviced. Soft-

ware can read the pin levels to identify which

pin(s) are the source of the interrupt.

If several input pins are selected simultaneously

as interrupt source, these are logically NANDed.

For this reason if one of the interrupt pins is tied

low, it masks the other ones.

s

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to

exit from HALT mode except those mentioned in

the 鈥淚nterrupt Mapping鈥?table.

A peripheral interrupt occurs when a specific flag

is set in the peripheral status registers and if the

corresponding enable bit is set in the peripheral

control register.

The general sequence for clearing an interrupt is

based on an access to the status register followed

by a read or write to an associated register.

Note:

The clearing sequence resets the internal

latch. A pending interrupt (i.e. waiting for being

serviced) will therefore be lost if the clear se-

quence is executed.

Same

SOFTWARE

PRIORITY

Different

HIGHEST SOFTWARE

PRIORITY SERVICED

HIGHEST HARDWARE

PRIORITY SERVICED

When an interrupt request is not serviced immedi-

ately, it is latched and then processed when its

software priority combined with the hardware pri-

ority becomes the highest one.

Note 1:

The hardware priority is exclusive while

the software one is not. This allows the previous

process to succeed with only one interrupt.

Note 2:

RESET and TRAP are non-maskable and

they can be considered as having the highest soft-

ware priority in the decision process.

Different Interrupt Vector Sources

Two interrupt source types are managed by the

ST7 interrupt controller: the non-maskable type

(RESET and TRAP) and the maskable type (exter-

nal or from internal peripherals).

Non-Maskable Sources

These sources are processed regardless of the

state of the I1 and I0 bits of the CC register (see

Figure 17).

After stacking the PC, X, A and CC

registers (except for RESET), the corresponding

vector is loaded in the PC register and the I1 and

I0 bits of the CC are set to disable interrupts (level

29/171