ST72260G, ST72262G, ST72264G

WATCHDOG TIMER

(Cont鈥檇)

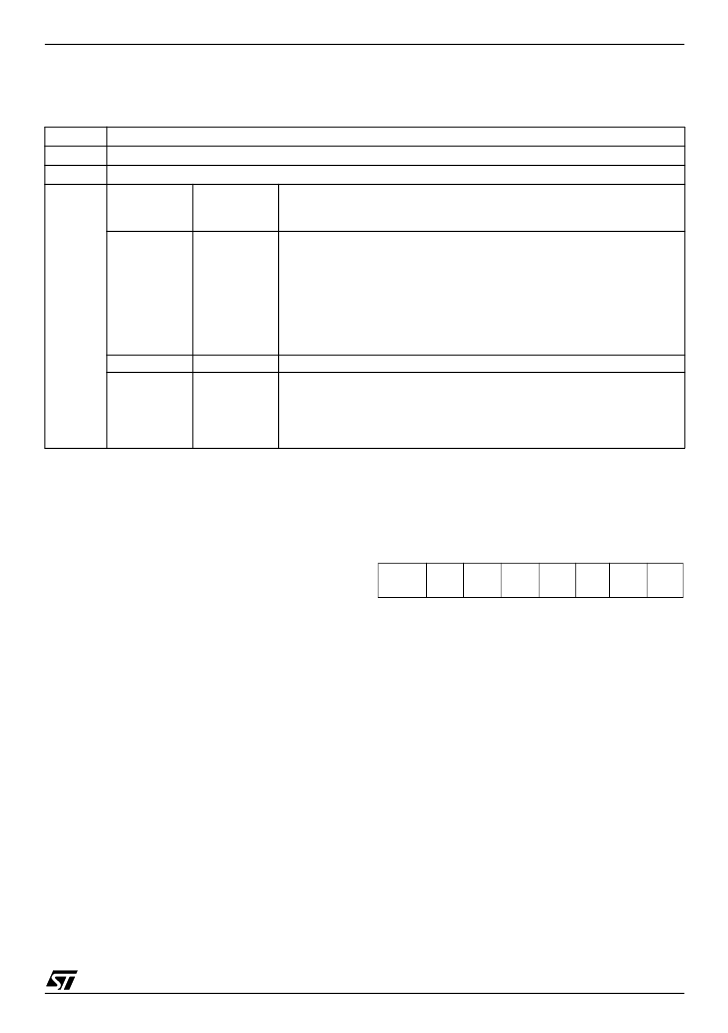

11.1.5 Low Power Modes

Mode

SLOW

WAIT

Description

No effect on Watchdog.

No effect on Watchdog.

OIE bit in

MCCSR

register

WDGHALT bit

in Option

Byte

No Watchdog reset is generated. The MCU enters Halt mode. The Watch-

dog counter is decremented once and then stops counting and is no longer

able to generate a watchdog reset until the MCU receives an external inter-

rupt or a reset.

If an external interrupt is received, the Watchdog restarts counting after 256

or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset

state) unless Hardware Watchdog is selected by option byte. For applica-

tion recommendations see

Section 11.1.7

below.

A reset is generated.

No reset is generated. The MCU enters Active Halt mode. The Watchdog

counter is not decremented. It stop counting. When the MCU receives an

oscillator interrupt or external interrupt, the Watchdog restarts counting im-

mediately. When the MCU receives a reset the Watchdog restarts counting

after 256 or 4096 CPU clocks.

0

0

HALT

0

1

1

x

11.1.6 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte,

the watchdog is always active and the WDGA bit in

the WDGCR is not used. Refer to the Option Byte

description.

11.1.7 Using Halt Mode with the WDG

(WDGHALT option)

The following recommendation applies if Halt

mode is used when the watchdog is enabled.

鈥?Before executing the HALT instruction, refresh

the WDG counter, to avoid an unexpected WDG

reset immediately after waking up the microcon-

troller.

11.1.8 Interrupts

None.

11.1.9 Register Description

CONTROL REGISTER (WDGCR)

Read /Write

Reset Value: 0111 1111 (7Fh)

7

WDGA

T6

T5

T4

T3

T2

T1

0

T0

Bit 7 =

WDGA

Activation bit.

This bit is set by software and only cleared by

hardware after a reset. When WDGA = 1, the

watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Note:

This bit is not used if the hardware watch-

dog option is enabled by option byte.

Bit 6:0 =

T[6:0]

7-bit counter (MSB to LSB).

These bits contain the value of the watchdog

counter. It is decremented every 16384 f

OSC2

cy-

cles (approx.). A reset is produced when it rolls

over from 40h to 3Fh (T6 becomes cleared).

51/171