Philips Semiconductors

SC16C654B/654DB

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 64-byte FIFOs

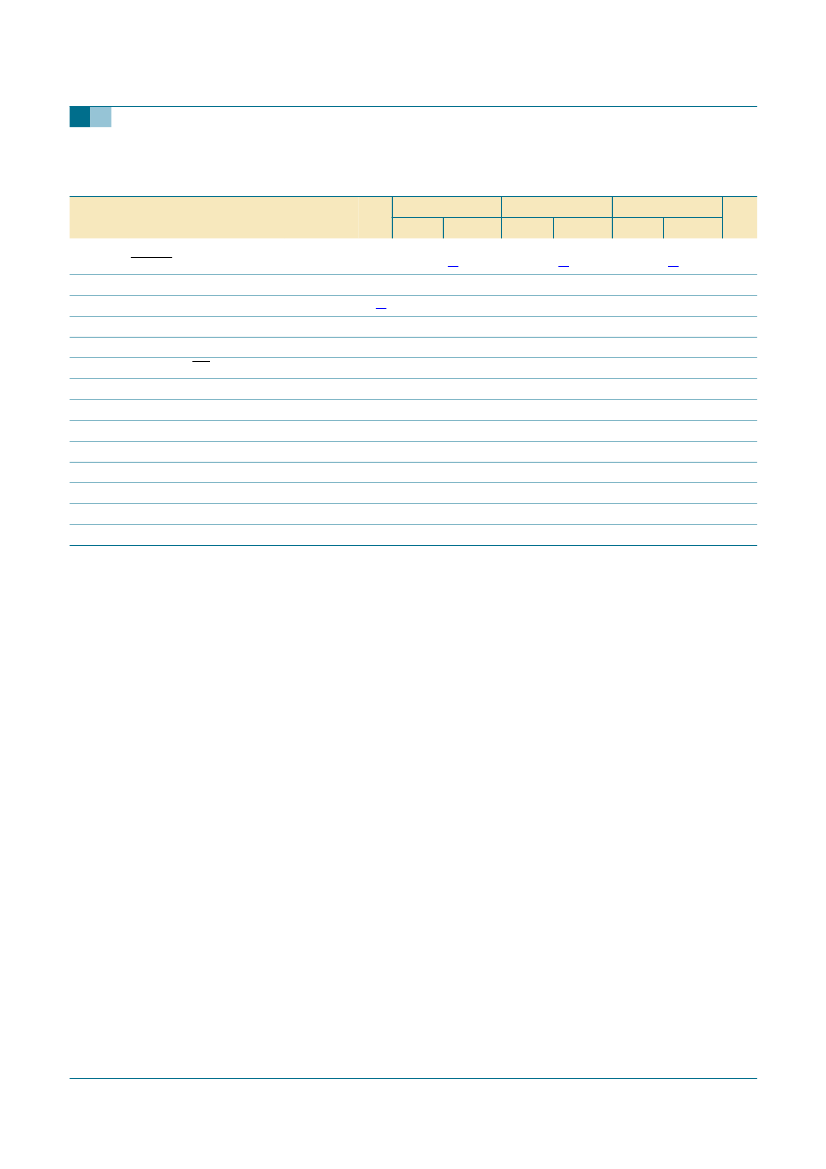

Table 28: Dynamic characteristics

鈥ontinued

T

amb

=

鈭?/div>

40

掳

C to +85

掳

C; tolerance of V

CC

=

卤

10 %, unless otherwise speci铿乪d.

Symbol

t

28d

t

30s

t

30w

t

30h

t

30d

t

31d

t

31h

t

32s

t

32h

t

32d

t

33s

t

33h

t

RESET

N

[1]

[2]

[3]

Parameter

delay from start to reset

TXRDY

address setup time

chip select strobe width

address hold time

read cycle delay

delay from CS to data

data disable time

write strobe setup time

write strobe hold time

write cycle delay

data setup time

data hold time

RESET pulse width

baud rate divisor

Conditions

-

10

25 pF load

25 pF load

25 pF load

25 pF load

[1]

V

CC

= 2.5 V

Min

[3]

V

CC

= 3.3 V

Min

-

10

26

15

20

-

-

10

10

25

15

5

40

[3]

V

CC

= 5.0 V

Min

-

10

23

15

20

-

-

10

10

20

15

5

40

[3]

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Max

8T

RCLK

-

-

-

-

90

15

-

-

-

-

-

-

Max

8T

RCLK

-

-

-

-

26

15

-

-

-

-

-

-

Max

8T

RCLK

-

-

-

-

23

15

-

-

-

-

-

-

(2

16

鈭?/div>

1)

90

15

20

-

-

10

10

25

20

15

200

1

(2

16

鈭?/div>

1) 1

(2

16

鈭?/div>

1) 1

Applies to external clock, crystal oscillator max 24 MHz.

Maximum frequency =

-------

RCLK is an internal signal derived from Divisor Latch LSB (DLL) and Divisor Latch MSB (DLM) divisor latches.

1

t

3w

9397 750 14965

漏 Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 02 鈥?20 June 2005

40 of 58