Philips Semiconductors

Product specification

3.3V Quad 2-input OR gate

74LVT32

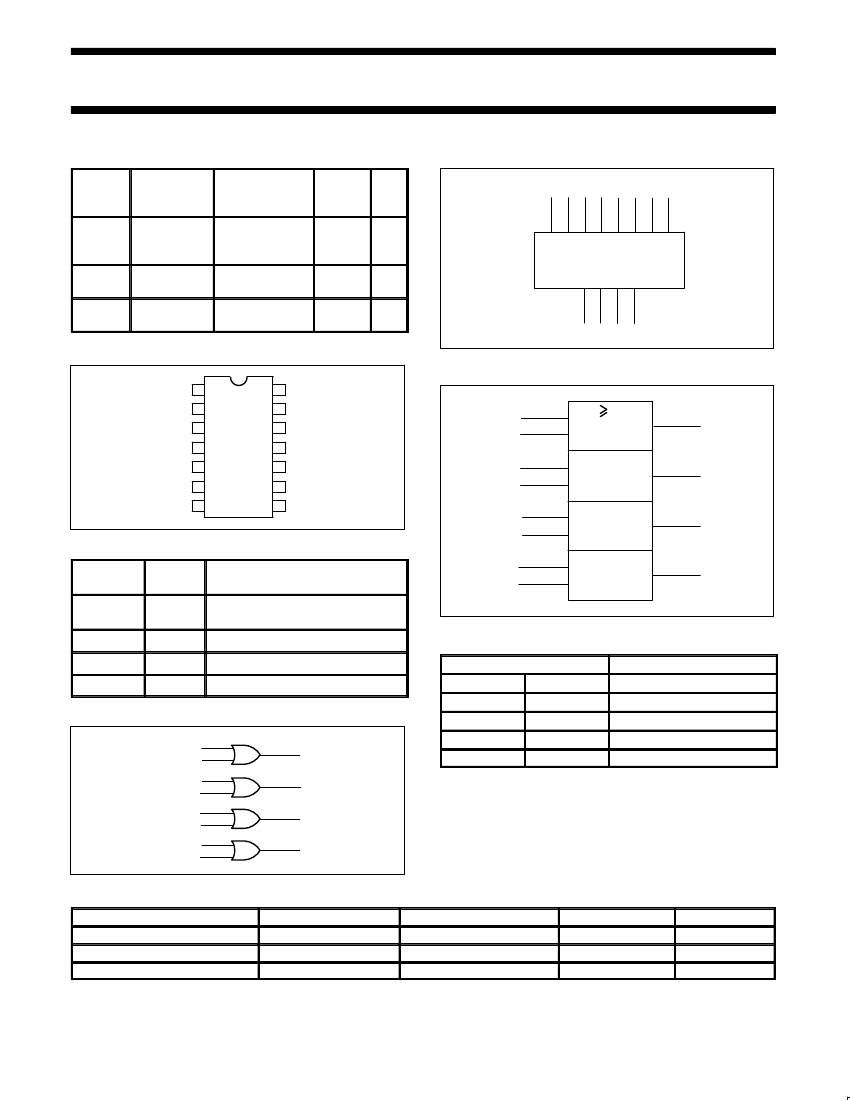

QUICK REFERENCE DATA

SYMBOL

PARAMETER

Propagation

delay

An, Bn to Yn

Input

capacitance

Total supply

current

CONDITIONS

T

amb

= 25掳C;

GND = 0V

C

L

= 50pF;

V

CC

= 3.3V

V

I

= 0V or 3.0V

Outputs Low;

V

CC

= 3.6V

TYPICAL

UNIT

LOGIC SYMBOL

1

2

4

5

9

10 12 13

t

PLH

t

PHL

C

IN

I

CCL

2.6

3.2

3

1

ns

A0 B0 A1 B1 A2 B2 A3 B3

pF

mA

Y0 Y1 Y2 Y3

V

CC

= Pin 14

GND = Pin 7

3

6

8

11

SA00355

PIN CONFIGURATION

LOGIC SYMBOL (IEEE/IEC)

A0

B0

Y0

A1

B1

Y1

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CC

B3

A3

Y3

B2

A2

Y2

4

6

5

1

2

1

3

9

SA00354

8

10

PIN DESCRIPTION

12

PIN

NUMBER

1, 2, 4, 5, 9,

10, 12, 13

3, 6, 8, 11

7

14

SYMBOL

An, Bn

Yn

GND

V

CC

NAME AND FUNCTION

Data inputs

Data outputs

Ground (0V)

Positive supply voltage

Dna

L

L

1

2

4

5

9

10

12

13

11

13

SF00041

FUNCTION TABLE

INPUTS

Dnb

L

H

L

OUTPUT

Qn

L

H

H

H

LOGIC DIAGRAM

A0

B0

A1

B1

A2

B2

V

CC

= Pin 14

GND = Pin 7

A3

B3

3

Y0

H

6

Y1

H

H

NOTES:

H = High voltage level

L = Low voltage level

8

Y2

11

Y3

SA00356

ORDERING INFORMATION

PACKAGES

14-Pin Plastic SO

14-Pin Plastic SSOP

14-Pin Plastic TSSOP

TEMPERATURE RANGE

鈥?0掳C to +85掳C

鈥?0掳C to +85掳C

鈥?0掳C to +85掳C

OUTSIDE NORTH AMERICA

74LVT32 D

74LVT32 DB

74LVT32 PW

NORTH AMERICA

74LVT32 D

74LVT32 DB

74LVT32PW DH

DWG NUMBER

SOT108-1

SOT337-1

SOT402-1

1996 Aug 28

2

853-1873 17244