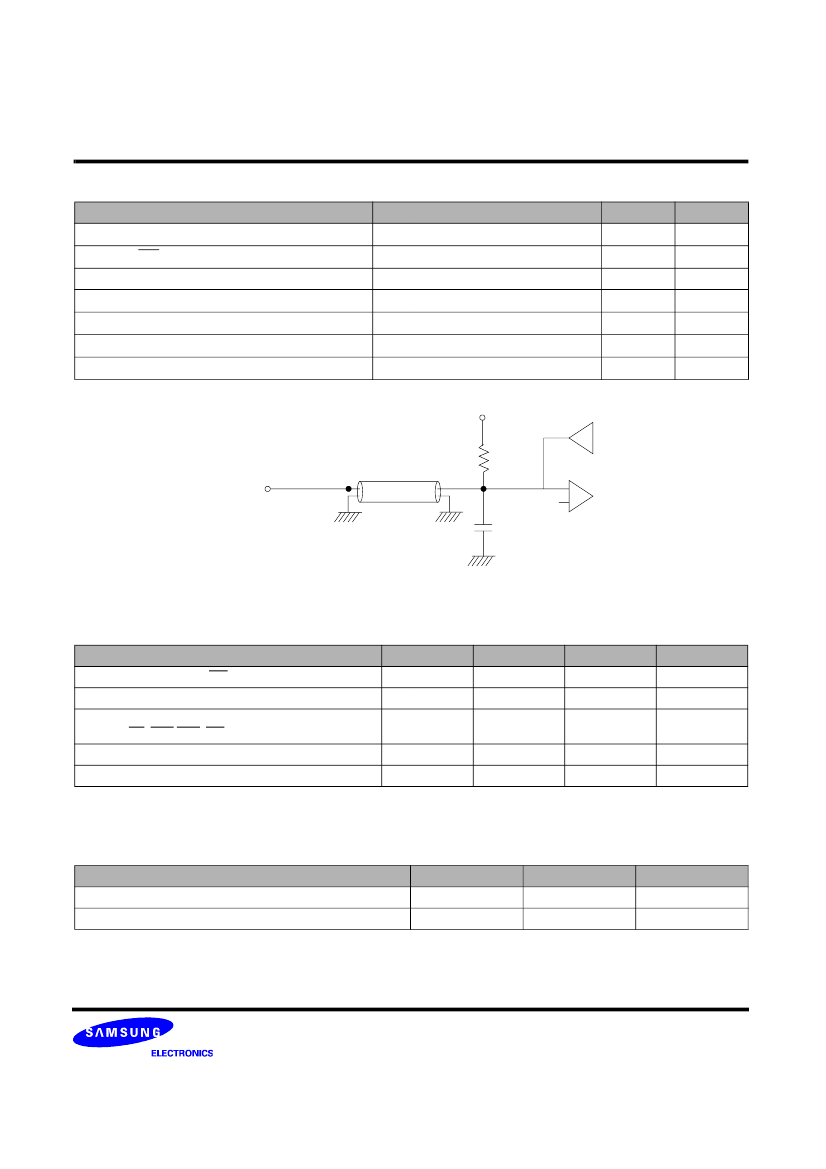

Z0=50鈩?/div>

V

REF

=0.5*V

DDQ

C

LOAD

=30pF

(Fig. 1) Output Load Circuit

CAPACITANCE

(V

DD

=2.6V, T

A

= 25掳C, f=1MHz)

Parameter

Input capacitance( CK, CK )

Input capacitance(A

0

~A

12

, BA

0

~BA

1

)

Input capacitance

( CKE, CS, RAS,CAS, WE )

Data & DQS input/output capacitance(DQ

0

~DQ

15

)

Input capacitance(DM0 ~ DM3)

Symbol

C

IN1

C

IN2

C

IN3

C

OUT

C

IN4

Min

1.0

1.0

1.0

1.0

1.0

Max

5.0

4.0

4.0

6.5

6.5

Unit

pF

pF

pF

pF

pF

DECOUPLING CAPACITANCE GUIDE LINE

Recommended decoupling capacitance added to power line at board.

Parameter

Decoupling Capacitance between V

DD

and V

SS

Decoupling Capacitance between V

DDQ

and V

SSQ

Symbol

C

DC1

C

DC2

Value

0.1 + 0.01

0.1 + 0.01

Unit

uF

uF

Note :

1. V

DD

and V

DDQ

pins are separated each other.

All V

DD

pins are connected in chip. All V

DDQ

pins are connected in chip.

2. V

SS

and V

SSQ

pins are separated each other

All V

SS

pins are connected in chip. All V

SSQ

pins are connected in chip.

- 12 -

Rev 1.7 (June 2004)