卤15kV ESD-Protected, 3.3V Quad

RS-422 Transmitters

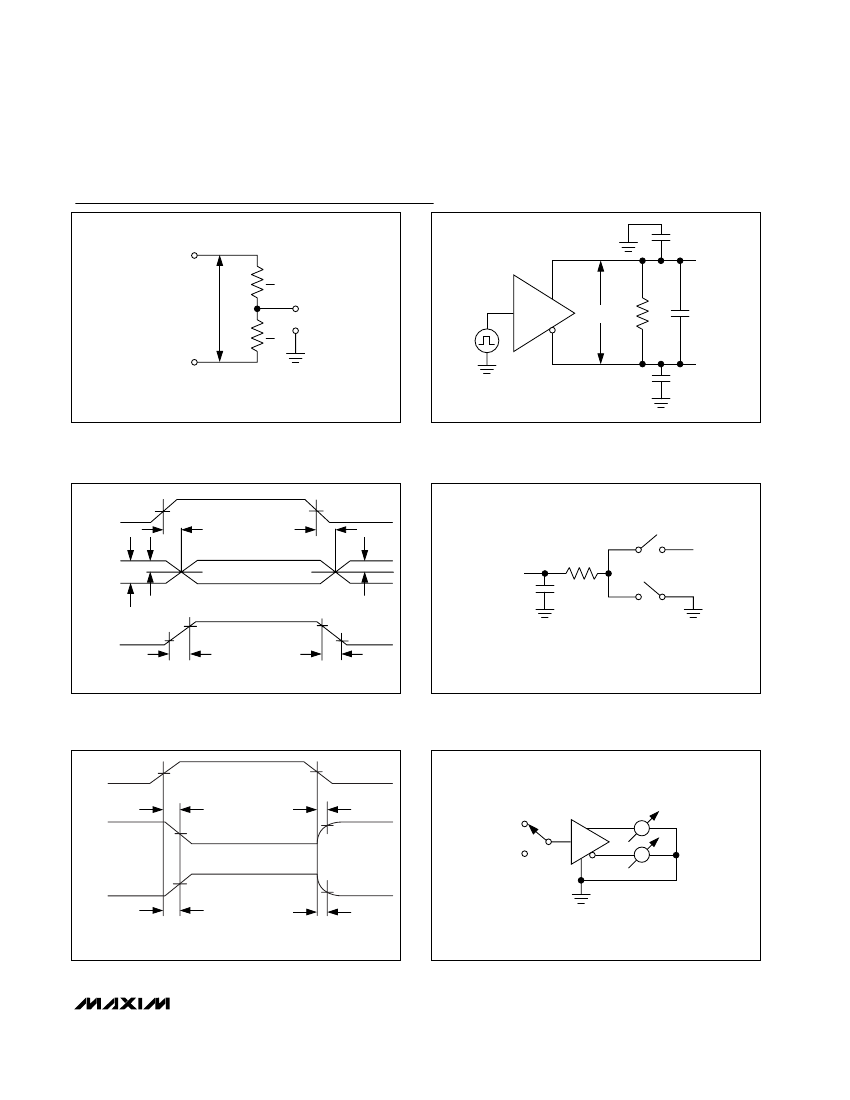

Test Circuits and Timing Diagrams

C

L

DI_+

R

L

2

V

OD

R

L

2

DI_-

C

L

DO_-

V

OC

DI_

V

OD

R

L

C

L

DO_+

MAX3030E鈥揗AX3033E

Figure 1. Differential Driver DC Test Circuit

Figure 2. Differential Driver Propagation Delay and Transition

Time Test Circuit

3V

DI

0V

1.5V

t

DPLH

t

DPHL

1.5V

1/2 V

O

R

L

C

L

1/2 V

O

V

DIFF

V

O

0V

-V

O

V

DIFF

= V (DO_+) - V (DO_-)

10%

t

R

90%

t

F

t

SKEW

= |t

DPLH

- t

DPHL

|

90%

10%

S2

ENABLE SIGNAL IS ONE OF THE POSSIBLE

ENABLE CONFIGURATIONS (SEE TRUTH TABLE).

S1

V

CC

DO_-

V

O

DO_+

OUTPUT

UNDER TEST

Figure 3. Differential Driver Propagation Delay and Transition

Waveform

Figure 4. Driver Enable/Disable Delays Test Circuit

3V

EN

0V

t

DZL

V

OL

V

OH

1.5V

0V

t

DZH

ENABLE SIGNAL IS ONE OF THE POSSIBLE

ENABLE CONFIGURATIONS (SEE TRUTH TABLE).

t

DHZ

t

DLZ

V

OL

+ 0.3V

V

CC

DI

GND

OUTPUT NORMALLY HIGH

V

OH

- 0.3V

DO_-

DO_+

A

A

1.5V

1.5V

1.5V OUTPUT NORMALLY LOW

Figure 5. Driver Enable/Disable Waveform

Figure 6. Short-Circuit Measurements

7

_______________________________________________________________________________________