鈥?/div>

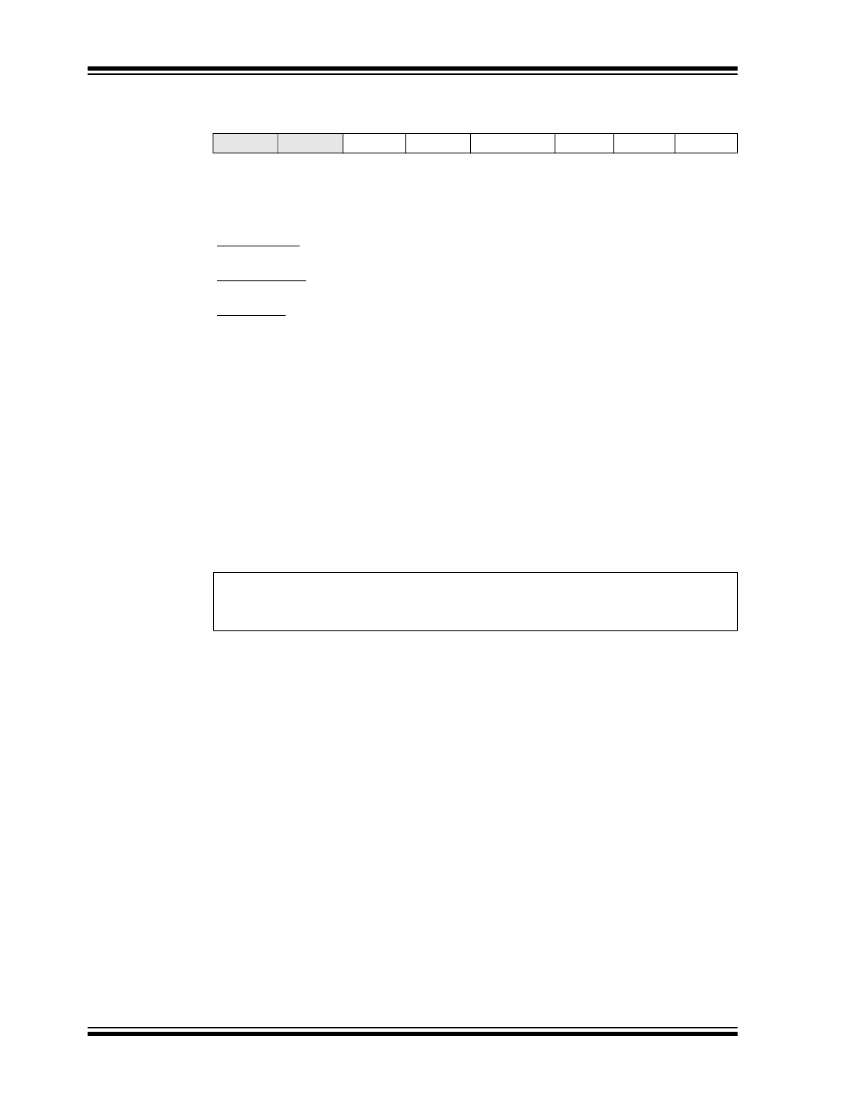

bit 7

bit 7-6

bit 5-4

Unimplemented:

Read as '0'

CCPxX:CCPxY:

PWM Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0

CCPxM3:CCPxM0:

CCPx Mode Select bits

0000

= Capture/Compare/PWM disabled (resets CCPx module)

0100

= Capture mode, every falling edge

0101

= Capture mode, every rising edge

0110

= Capture mode, every 4th rising edge

0111

= Capture mode, every 16th rising edge

1000

= Compare mode, set output on match (CCPxIF bit is set)

1001

= Compare mode, clear output on match (CCPxIF bit is set)

1010

= Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is

unaffected)

1011

= Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);

CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module

is enabled)

11xx

= PWM mode

Legend:

R = Readable bit

-n = Value at POR

W = Writable bit

鈥?鈥?= Bit is set

U = Unimplemented bit, read as 鈥?鈥?/div>

鈥?鈥?= Bit is cleared

x = Bit is unknown

U-0

鈥?/div>

R/W-0

CCPxX

R/W-0

CCPxY

R/W-0

CCPxM3

R/W-0

R/W-0

R/W-0

bit 0

CCPxM2 CCPxM1 CCPxM0

DS30605C-page 50

铮?/div>

2000 Microchip Technology Inc.