32 Mbit Concurrent SuperFlash + 4 Mbit SRAM ComboMemory

SST34HF3244C

Data Sheet

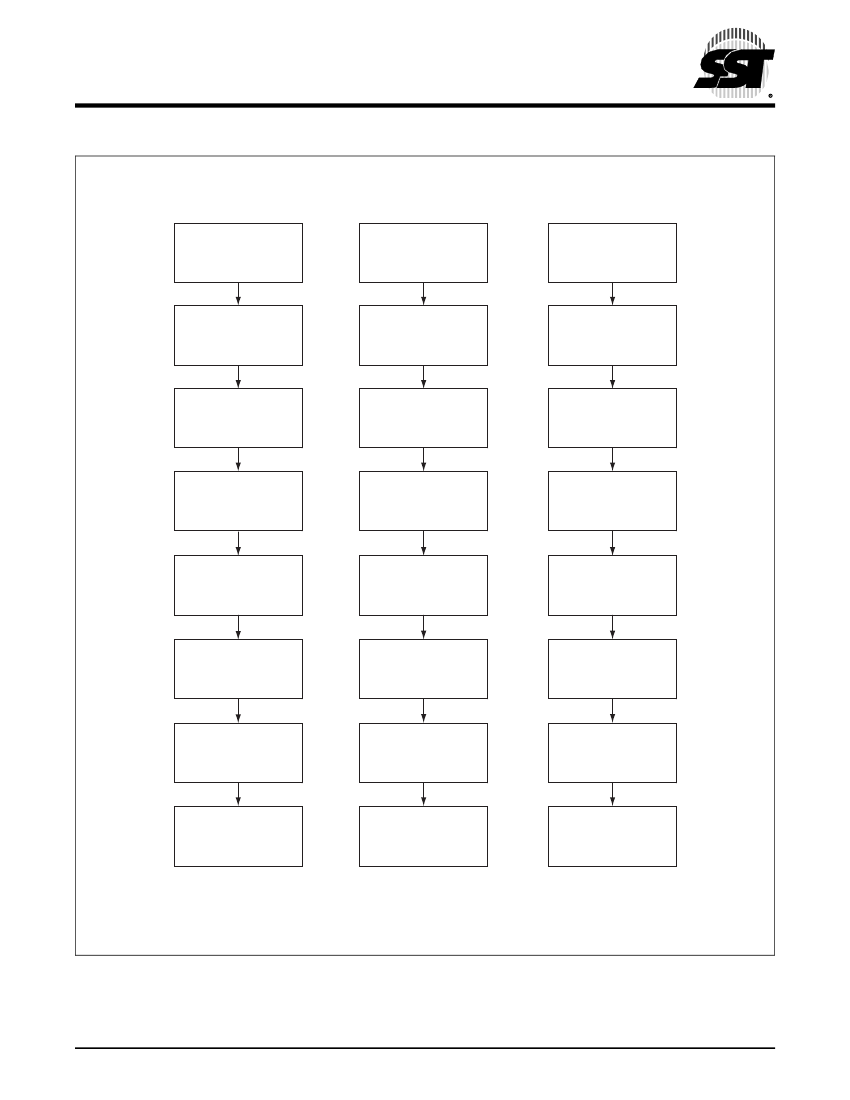

Chip-Erase

Command Sequence

Load data: XXAAH

Address: 555H

Sector-Erase

Command Sequence

Load data: XXAAH

Address: 555H

Block-Erase

Command Sequence

Load data: XXAAH

Address: 555H

Load data: XX55H

Address: 2AAH

Load data: XX55H

Address: 2AAH

Load data: XX55H

Address: 2AAH

Load data: XX80H

Address: 555H

Load data: XX80H

Address: 555H

Load data: XX80H

Address: 555H

Load data: XXAAH

Address: 555H

Load data: XXAAH

Address: 555H

Load data: XXAAH

Address: 555H

Load data: XX55H

Address: 2AAH

Load data: XX55H

Address: 2AAH

Load data: XX55H

Address: 2AAH

Load data: XX10H

Address: 555H

Load data: XX50H

Address: SAX

Load data: XX30H

Address: BAX

Wait TSCE

Wait TSE

Wait TBE

Chip erased

to FFFFH

Sector erased

to FFFFH

Block erased

to FFFFH

1282 F21.0

Note:

X can be V

IL

or V

IH,

but no other value.

FIGURE 26: Erase Command Sequence

漏2006 Silicon Storage Technology, Inc.

S71282-02-000

8/06

37