如何让数字硬件设计简单化

出处:维库电子市场网 发布于:2017-08-08 17:41:00

VHDL和Verilog是用于描述可综合数字硬件的两种主流语言。但我们不应忘记,它们初可不是为了这个目的创建的,而是为了模拟和归档。这个事实加之许多其它语法弱点,引发了许多问题,比如设计参数化能力弱;设计可重用性差;代码冗长、方法繁复;以及使可综合和不可综合特征之间的边界模糊不清。为了应对这些限制和问题,一些新的替代解决方案已经出现,如Bluespec、Chisel、CλaSH、Migen、MyHDL和SpinalHDL等。

以不同方式描述硬件

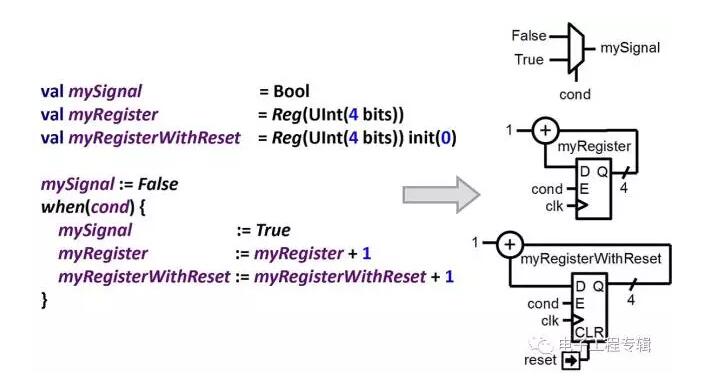

与VHDL和Verilog一样,SpinalHDL可用于通过定义寄存器和门来描述硬件,SpinalHDL不使用众所周知的事件驱动范式来描述硬件(如VHDL和Verilog),而是使用专为此目的设计的语法。这允许在其声明中区分组合信号与寄存器,并通过定义规则来描述硬件行为。这意味着信号和寄存器可以在相同的条件语句中分配,而这对于“事件驱动”替代方案是不可能的(见图1)。

图1:简单的硬件描述。

语言的所有语法都可用于硬件描述,语法可分为两类。一类是:通过使用专用类型显式(explicitly)定义可综合硬件;另一类是:可用于阐述硬件结构,例如实例循环、功能和类。除此之外,SpinalHDL编译器将执行许多检查,以确保用户设计是合法的,例如:是否缺少组合循环;所有组合分配的完整性、以避免不必要的闩锁指推(inferring unwanted latche);跨时钟域连接的合法性等——这使得SpinalHDL用起来很安全。

但SpinalHDL与VHDL和Verilog的主要不同是其嵌入到通用语言(Scala)中这一事实。由于这种方法,我们得到一个“Meta HDL”,其中高层级部分(类、动态阵列、字典...)可用于通过算法手段生成可综合的硬件描述。这提供了非常高的表现力来描述灵活和可重复使用的硬件。实际上,正是它使SpinalHDL有能力以面向对象和功能性编程的方式来操纵所描述设计的每一个元素;它与一个有能力的标准库结合起来,从而在元硬件描述和阐述能力方面获得了出乎意料的能力,远超VHDL、Verilog和SystemVerilog所能(见图2)。

图2:使用抽象实现寄存器库(register bank)。

SpinalHDL编译器能够将用户编写的硬件描述转换为人类可读和可综合的VHDL/Verilog网表(正如大多数原理图输入工具贯穿所用),这使得它已经与行业中使用的大多数EDA工具兼容。

此外,目标语言/EDA工具不须本地支持Spinal-HDL提供的所有功能(例如类型和数据结构参数化),在被解压缩/展开到生成的VHDL/Verilog网表前,在SpinalHDL编译器内部得以支持、解决(见图3)。

图3:仲裁管道的实现。

未来展望

作为这些概念的现实演示者,我们使用SpinalHDL实现了一款名为“Pinsec”的小型SoC,它集成了RISC-V CPU、SDRAM控制器、嵌入式RAM、GPIO、定时器、UART、VGA和JTAG调试接口,由AXI4和APB3互连全部连接在一起(见图4)。

图4:Pinsec SoC框图。

该演示表明,可非常容易地实现设计的顶层,特别是在涉及总线互连的参数化和实例化时。 与传统方法不同,SpinalHDL只需几行代码就能搞定,从而大大提高了可读性和生产率。例如,将新外设连接到APB互连只需要一行参数化代码(见图5)。

图5:Pinsec的总线桥和所有APB3总线构造的顶层实例化。

另一个有趣的演示是RISC-V CPU(名为VexRiscv)的第二次迭代,演示了使用SpinalHDL的先进元硬件描述功能带来的增益。首先,CPU顶层是一个空白骨架,它只提供一些阐述服务、作为信号通过各阶段(stage)的自动流水线、以及各阶段的仲裁接口。

与一个允许在CPU顶层注入硬件的插件注册系统相结合,该方法支持——可以具有相同功能的多个变体、而无需将其集成到CPU代码中的——非常灵活的CPU架构。插件可从简单的事情(例如程序计数器或整数ALU)到复杂的操作(例如通过L1缓存的加载和存储支持)。

插件之间的合作也可能非常复杂。例如,所有插件都可以发布新的指令操作码,以及如何由指令解码器进行解码。

然后,指令解码器将使用与SpinalHDL元硬件功能相结合的Quine-Mc Cluskey算法来生成指令解码逻辑。

结论

使用SpinalHDL是改变数字硬件设计愿景并实现真正工程化的一种体验。凭借其所有功能,它允许芯片设计人员描述优雅和可重复使用的硬件,而没有通常使用的HDL(如VHDL、Verilog甚至System-Verilog)的繁琐和限制。它也证明了使用软件工程技术在生成的RTL中没有任何开销就可详细描述硬件结构的可行性和收益。该语言及其参考编译器也是完全和开源的。

,请注意:上述示例中使用的所有功用和类,如Stream、RGB、队列、Apb3Decoder、AxiLite4和AxiLite4SlaveFactory都不是Spinal-HDL语言中提供的功能,而是由标准库使用其常规语法提供。换句话说,可以通过实现新的库、抽象层和可从根本上改善硬件描述表现力的工具来扩展语言本身;也可在不忽视抽象硬件的条件下、通过引入新的概念来扩展语言(因为这些库仍然在RTL域内实现)。

下一篇:初学PLC的几种方法

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 电气负载模拟器2024/9/12 17:08:40

- 了解变压器耦合电压开关 D类放大器2024/9/12 16:41:27

- 电位计的模拟2024/9/4 16:20:18

- 运算放大器总结2024/9/3 16:44:04

- 光耦合器替代方案2024/9/2 16:44:33