基于BIST利用ORCA结构测试FPGA逻辑单元的方法

出处:电子设计 发布于:2018-11-29 14:53:38

现场可编程门阵列FPGA(Field ProgrammableGate Array)是一种新型器件,它将门阵列的通用结构与现场可编程的特性结合于一体,因而受到广泛关注。FPGA 测试中,测试激励的多种测试生成方法,都有其一定局限性,不能求出所有故障,而且随着集成电路规模的迅速膨胀,电路结构也越来越复杂,大量的故障变得不可测。所以,人们把视线转向了电路系统的设计过程。如果设计的电路容易测试,容易找到测试码,对测试和测试码的生成问题就大大简化,这就是可测性设计问题。可测性设计问题的一个主要解决方法就是内建自测法BIST(Built-in self-test)。

FPGA可重复编程的特性,通过脱机配置,建立BIST逻辑,即使由于线路被操作系统的重新配置而令BIST结构消失,可测性也可实现。本文给出一种基于BIST利用ORCA(Optimized Reconfigurable Cell Array)结构测试FPGA逻辑单元PLB(Programmable Logic Block)的方法,该方法对逻辑单元PLB 进行了分类、分阶段的测试,同时进行电路模拟实验。

BIST测试结构

这种基于BIST的测试方法是一系列测试阶段顺序进行的结果,每一阶段都包括以下几步:1)对电路进行配置;2)测试初始化;3)生成测试图形;4)对响应进行分析;5)读出测试结果。

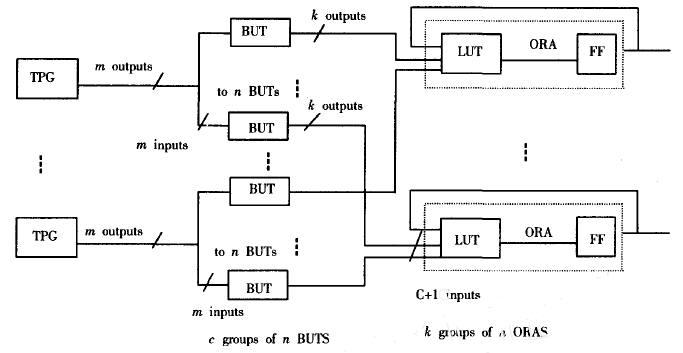

图1 给出了利用ORCA测试方法过程中FPGA的配置结构。在用于完全测试BUT (Block Under Test)的绝大部分配置中,TPG以二进制计数器的模式工作,为BUT的m个输入端提供随机的测试模式。由于PLB的输入要多于输出,所以需要将一些PLB通过编程构造成m位的计数器,在存储器的操作模式中,存储器被配置为随机存储器。TPG作为p字节(p

图1 测试FPGA的ORCA结构

不同的TPG一定要满足BUT的需求,BUT的输出要与ORA相符合,因此,TPG的数目要求为c,c同时也是与一个ORA相符合的PLB的输出管脚数。ORA由一个LUT和一个触发器组成,其中LUT用于从c 组BUT 相应的输出作比较,触发器记录次不匹配的情况。从触发器输出到LUT 输入的反馈信息会在ORA次错误记录之后进一步做比较。通常,一些ORA会在同一个PLB中实施,这依赖于PLB中相互独立的LUT的个数。这里,如果LUT的输入序列至少与一个PLB 是分离的,则认为此LUT是独立的。每一个TPG驱动一组共n个BUT,每个BUT有m个输入和k个输出,则BUT中共有c*n*k个输出与k 组n个ORA作比较,每个ORA监控c个输出,ORA的第i组接收n个BUT的第i个输出。

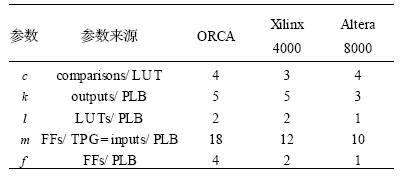

例如,在ORCA结构的PLB中,存在2个独立的LUT,每个LUT 有5个输入,由于反馈的存在,需令c=4。又由于每个PLB有18个输入,TPG生成随机测试向量所要求的触发器的数量也是18。因为一个PLB中有f=4个触发器,所以需要5个PLB来构成随机TPG,其中只有4个PLB是用于产生RAM模式测试进而构成TPG状态机的。,每个必须与ORA作比较的PLB中有k=5个输出。表1对以上数据进行了概括,并将Xilinx 4000与Altera Flex 8000系列中的FPGA各项参数进行了对比,对FPGA这些结构参数、TPG输出信号计数n以及BIST所需步骤的数目进行了分析。多数商业用途的FPGA进行完全测试需两个测试步骤,而一些其他规模的FPGA则需要三个步骤。

测试实施

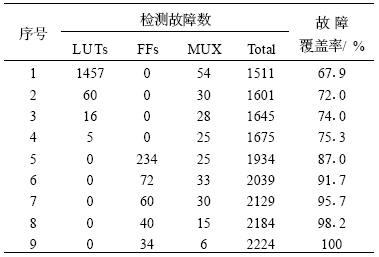

在测试实施阶段利用故障模拟来评价不同BIST步骤中的故障覆盖率。为ORCA结构的PLB建立了一个完全的门级电路模型,包括代表基本输入值的PLB配置,那些输入值在每一阶段是“固定”的。允许模拟影响配置位的stuck-at故障。LUT、FF和Output Mux三个模组中每一个的随机测试用于检测无法探查的故障(LUT中为3个故障,FF中为4 个故障),这些故障从故障目录表中被移除。PLB中共2224个stuck-at门级故障,其中1538个在LUT中,440个在FF 中,224个在输出MUX中,完全测试每个PLB共需9次这样的配置结构。对3个模组中每一阶段所检测出的新故障数目、检测故障累积的总数及故障覆盖率等故障模拟结果见表2。

表1 FPGA结构参数对比

表2 PLB故障模拟测试结果

从表2中可以看出,阶段为LUT提供了一个完全的测试,而接着的5个阶段检测了FF中所有的故障,对输出MUX所有的故障检测需要9步。这9次配置结构可以根据为三个模组中每一个而设定的模式来描述。一个ORCA输出利用9*1 MUX来选择4个LUT输出中的任一个,或者4个FF输出的任一个,也就是LUT在以快速加法器操作方式进行工作。这9*1MUX证实了完全测试输出MUX 块的配置数量。

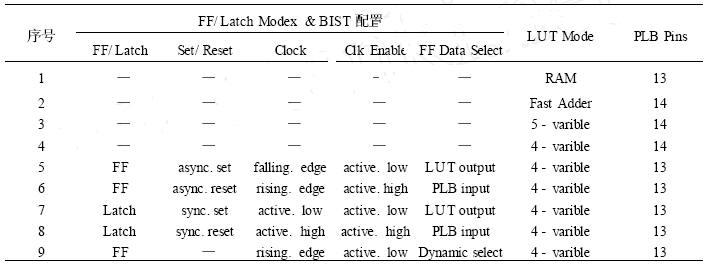

ORCA结构的LUT有4个不同的操作模式:RAM、fast adder 、5 变量的LUT-based逻辑功能、4变量的LUT-based逻辑功能。它们在PLBBIST前4步中进行测试,如表3所示。在RAM模式中,TPG被配置为产生标准RAM 测试序列,而在其他步骤中被配置为二进制计数器。一旦LUT已经在RAM模式下测试,余下的BIST步骤中,依靠LUT中的棋盘模式来确定LUT输出的所有可能模式。FF有以下操作模式供选择:1)FF/Latch;2)Set/Reset;3)falling edge/rising edge ofclock等,与这些选择相关的数据太大,不易考虑。因此,可根据对PLB 门级电路模型的故障模拟来选择。5 次配置对完全测试FF 模组是足够的。

表3 PLB BIST配置

从表3的后半部分可知FF 模组各种操作模式的不同选择情况。在这9次BIST配置中,ORCA的典型应用包括54%的连线资源可编程线段以及87%的PLB和LUT。尽管多数ORCA只需要2个测试阶段,还需18次的配置结构来测试所有的PLB。这18次配置结构与通常应用ORCA结构测试的32次配置相比,结果比较令人满意。

测试中遇到的问题

路线资源的限制

作为伪随机测试,PLB的测试包括PLB大多数的I/0管脚,但IC系列ORCA路由于资源有限,不能支持所有TPG输出到BUT以及所有的BUT输出到ORA。为解决这个问题,基于伪随机测试的准则允许对每配置有一点“偏差”,只对在该阶段确实用到的输入采用随机测试,并观察其输出。表3给出了每一步BIST所用到的PLB管脚数目,路线资源可以满足系统要求。

缺少详细的配置控制

在一般的应用中,用户只需要将FF的输出与PLB的输出相连,而不管是具体哪个输出,这是特定的布线算法和路由算法决定的。在本方法中,为了得到完全的测试,必须保证每一个输出矩阵依次与它的9个输入(4个FF输出,4个LUT输出,1个加法器进位)相连,因此有一种与这9次配置都不同的选择。但是CAD工具不允许用户控制输出的多路复用器(用户模式下没有输出多路开关),因此,解决方法是修改中间的设计文件或者配置位流,来控制输出的多路输出选择。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- EPS Global - 谁需要嵌入式安全?2024/4/22 15:39:31

- 什么是嵌入式SoC2024/4/3 16:20:28

- EasyARM-i.MX283(7)A 默认供电方案2024/3/28 17:39:53

- EasyARM-i.MX283(7)A 的快速入门2024/3/27 17:29:30

- 非线性数字滤波器:用例和示例代码2024/3/14 16:34:20

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命