HDL仿真器基于事件的仿真算法

出处:维库电子市场网 发布于:2023-06-20 16:47:38

目前,HDL仿真器主要有三种实现算法(机制):基于时间的算法(Time-Based)、基于事件的算法(Event-Based,EBS)和基于周期的算法(Cycle-Based,CBS)

基于时间的算法适合处理连续的时间及变量,其会在每一个时间点对所有的电路元件进行计算。但是,在大部分情况下,每一个时间点只有约2%~10%的电路处于活动(运行)状态,所以该算法效率非常低。

基于事件的算法适合处理离散的时间、状态和变量。该算法只有在电路状态发生变化时才进行处理,只仿真那些可能引起电路状态改变的元件。仿真器响应输入引脚上的事件,并将值在电路中向前传播。目前来说,该算法效率,且应用为广泛,大部分的商业仿真器都是基于该种算法进行开发的。用某仿真器厂家的宣传语,就是“Evaluate When Necessary”。

基于周期的仿真算法以时钟周期为处理单位(与时间无关)。其旨在时钟边沿进行计算,不管时钟周期内的时序,且只是用两值逻辑(0和1)。该算法主要针对的是大规模设计(尤其是数字IC设计),且只能应用于同步电路。

下面详细介绍一下基于事件的仿真算法:

仿真器在编译数据结构时建立一个事件队列;

只有当前时间片中所有事件都处理完成之后,时间才能向前;

仿真从时间0开始,而且时轮只能向前推进。只有时间0的时间处理完后才能进入下一时间片;

在同一个时间片内发生的事件在硬件上是并行的;

理论上时间片可以无限,但实际上受硬件(如电脑的CPU等)和软件(如该仿真软件是否支持多线程技术等)的限制。

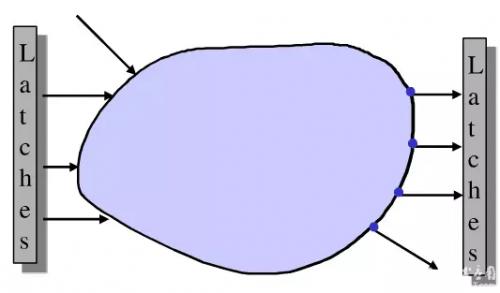

而基于周期的算法只会在时钟的边沿来计算组合逻辑的输出结果,因此基于周期的算法速度更快,内存的使用效率更高。同时,因为基于周期的算法不允许进行严格的时间约束,所以其仿真时间没有基于事件的算法高(since cycle-based simulators do not allow detailed timing specificity, they are not as accurate. )。基于周期的算法的原理图,如下图所示:

基于事件的算法,基于周期的算法和传统的电路仿真软件SPICE的比较图:

目前基于事件的算法的仿真器(EBS Simulator)主要有:

Modelsim、ActiveHDL、NC-Verilog、Verilog-XL、VCS(Verilog)、Scirocco(VHDL)等。

基于周期的算法的仿真器(CBS Simulator)主要有:

Modelsim、Synopsys Cobra等。

其中Modelsim同时支持EBS和CBS。

上一篇:编程器电源过流保护设计

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 光耦详细应用教程2024/4/26 16:43:32

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”2024/4/26 15:56:19

- 可控硅的工作原理、分类、作用与三极管的区别、与场效应管区别、典型应用接线图2024/4/24 17:56:03

- N型和P型半导体的导电特性2024/4/24 17:34:41

- NPN与PNP的基础知识介绍2024/4/23 17:48:16

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命