电子工程师的测量“神器”——任意波形发生器如何设计?

出处:电子技术设计 发布于:2019-06-21 14:26:07

任意波形发生器设计中非常重要的是所用的ADC、DAC、运放、时钟以及电源等,这些器件正确选型能确保系统能提供较低的杂散、噪声以及其他关键指标。模拟技术厂商ADI近上线的全新任意波形发生器解决方案设计参考,侧重于带宽300MHz以下的应用场合,利用ADI先进的DAC技术,提供了较低的杂散和噪声指标,能够解决用户在芯片选型上的困惑,也可以提前预知设计难点,在前期设计中就可以做好应对措施。

任意波形发生器六大设计痛点如何破?

任意波形发生器是现代电子测试领域应用为广泛的通用仪器之一,它利用高速DAC将内存中的波形文件转换为实际的波形信号,其波形文件可以由用户灵活定制,波形特征仅受限于其采样率带宽。由于各种干扰的存在以及环境的变化,实际运行在实际电子环境中的设备,电路中往往存在各种信号缺陷和瞬变信号,例如过脉冲、尖峰、阻尼瞬变、频率突变等。任意波形发生器可以产生各种理想及非理想的波形信号,因此可以用于各类半实物仿真中。例如汽车碰撞实验的复现,或者产生高速模拟信号来测试某种芯片的功能。从简单的正弦波产生到复杂一点的AM/FM调制信号,再到更加复杂的QAM调制信号等都有着任意波形发生器的应用。

以往的波形发生器大都采用了DDS(Direct Digital synthesizer,直接数字式频率合成器)技术,这种技术由美国学者J.Tiemey、C.M.Rader和B.Gold于1971年首次提出。但是由于DDS芯片内部的数据结构等都是固定的,不容易改变,使得输出波形的种类有限,系统的可配置性和灵活性也被受到了限制,而且功耗还是比较大、成本也比较高。后来,伴随着现场可编程门阵列FPGA技术的日益发展,越来越多的人开始关注利用FPGA技术来完成任意波形发生器的设计。而在设计的过程中,以下六个设计难点值得特别注意:

高速大幅度

高速运放很多,但是能输出大幅度的很少,所以有些高速信号放大电路需要借助分立三极管来实现,这样就使得设计难度大大增加。

平坦的通带特性

通带平坦度不够好会导致波形失真,正弦波可以用幅度补偿来优化平坦度,但是任意波形是做不到这一点的,所以一款性能的信号源,它的硬件电路一定是有着出色的平坦度指标。

低噪声

想要产生1mVp-p甚至更小幅度的信号,信噪比指标是绕不过去的问题,需要至始至终考虑到整个产品的设计中去。

低抖动的方波、脉冲波

纯DDS架构产生的方波会在非fsa/n频率输出时,有着多1/fsa的抖动,那是巨大的可见的抖动,所以通常是不能被接受的,必须通过一些特殊的方式来去除这种抖动。使用可变采样率的逐点输出波形发生器不存在这个问题。

触发通道与模拟通道之间的抖动

触发输出与模拟通道输出之间的抖动主要来自于数字信号和模拟信号的对齐问题。触发输出来自FPGA产生的数字信号,当非fsa/n频率输出时,它是无法与模拟信号相位过零点对齐的,所以会产生周期性抖动。触发输入与模拟通道输出之间的抖动是由于外部触发输入信号是随机的,它多数情况下无法对齐FPGA采样主时钟,所以从触发信号采样转换到模拟输出有着明显的抖动。

两通道相位对齐

原本来自同一时钟芯片的时钟供给两个DAC,layout时延控制好一点,容易实现两个通道的相位同步。但实际上高速DAC内部有DLL,每次上电之后的初始相位可能会发生变化,所以想要做到ps级别的相位对齐依然是比较有挑战性的。对于这个问题,使用双通道的DAC要简单很多,但是通道隔离度的指标可能会变差。

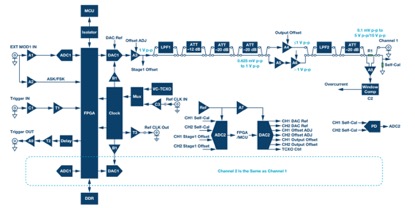

ADI高性能任意波形发生器是这样的

ADI提供参考的任意波形发生器系统框图是常见的基于DDS架构的FPGA+DAC。例如要实现2.5GSPS的AWG,就需要在FPGA内部并行运行10组DDS,每组DDS的时钟为250MHz,每组初始相位间隔36度,每组DDS都使用相同的波形查找表LUT,把生成的数据并串转换合成2组高速的1.25Gbps14通路的LVDS数据发送给DAC。

AWG通常对信号的抖动指标要求颇高,所以推荐超低抖动的时钟芯片,例如LTC6952或者HMC7044。如果AWG要设计成通道浮地输出的话,那么MCU适合放在接大地的机壳地端,那样可以简化GPIB/USB/LCD等对外接口(无需隔离设计)。AWG浮地输出能力是一种相对比较安全的设计,哪怕被测物(DUT)不是工作在以大地为参考电平之上的,也不会损坏DUT或者AWG自身。

触发输入输出端口的设计有一定的难度,主要体现在如何去除和模拟通道输出信号之间的抖动。触发输入信号端口有可能是个模拟信号,所以需要高速比较器来转换成数字电平,例如ADCMP605,直接差分输出给FPGA,可以减少过长信号路径导致对模拟通道的串扰。

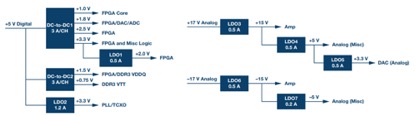

而该AWG的电源拓扑则主要以高整合度和低噪声的电源芯片为主。对于任意波形发生器这类信号源产品要求噪声越低越好,信噪比越高越好。然而供电多数来自ac至dc或者dc至dc电源,本身就有很多的开关噪声和高频尖刺,所以对于LDO的选择主要考量PSRR指标,是选择有宽频抑制能力的,那样就可以抑制dc至dc的纹波和其谐波。比较推荐的一颗LDO是LT3045-1,它在10MHz处依然有着50dB以上的PSRR。对于供电电流比较大,电压路数也比较多的FPGA应用场合,推荐选用LTM4643/LTM4644这样的电源模块,简化layout面积和设计难度,一片就可以满足多数FPGA的供电需求。

结论

随着通信技术、雷达系统的不断发展,对信号源的频率稳定度、频谱纯度、频率范围和输出频率的个数以及信号波形的形状也提出越来越多的要求。任意波形发生器不仅能产生正弦波、方波等标准波形,还需要根据需求产生任意波形,输出波形质量好,频率范围宽,频率稳定度、准确度及分辨率高,频率转换速度快且频率转换时输出波形相位连续等。

上一篇:三极管和场效应管测量

下一篇:准确测量开关损耗

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试2024/4/26 17:31:11

- 定义绝缘耐久性评估的电压脉冲测试要求2024/4/26 16:36:19

- Keysight - 是德科技联合 ETS Lindgren 推出创新 NB-NTN OTA 测试解决方案2024/4/25 15:59:02

- 三坐标测量仪使用步骤及注意事项2024/4/11 17:54:47

- 如何提高接地电阻2024/4/11 16:38:47

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命