嵌入式掉电保护电路

出处:rj17 发布于:2011-05-01 00:00:00 | 2627 次阅读

下图是一种典型的嵌入式系统硬件设计方案。系统的微处理器采用S3c4510B,是基于ARM7体系结构的。SDRAM是一种易失性存储器作为程序的运行空间,类似于PC机的内存;Flash作为程序存储空间是非易失性的。程序运行过程中的数据往往缓存在sDRAM中,在系统失电时必须写往Flash。

典型的嵌入式系统硬件设计方案

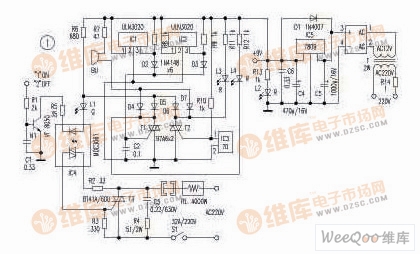

在系统中,需要使用5V和3.3V的直流稳压电源。其中,S3C4510B及部分外围器件需3.3V电源,另外部分器件需5V电源。为简化系统电源电路的设计,要求整个系统的输入电压为高质量的5V的直流稳压电源。有别于一般的电源回路设计,本系统的电源回路设计过程中增加了有关掉电保护的设计。包含这个设计的系统电源电路如下图所示。

电源电路

这个电源回路除了可以提供5v和3.3v的电源以外,还为系统掉电保护提供了延时及预警功能,通过软件的配合可以实现系统的掉电保护机制。正常情况下,由供电回路1给整个系统供电。当系统由于意外原因掉电时,由于输入的比较电压降低,这样MAX809 模块输出电压产生翻转为系统提供掉电中断预警信号,中断请求通过外部中断引脚XREQ0产生;同时供电回路2开始启用。通过大电容C3、c4放电,继续为系统提供一段供电电压,支持掉电中断服务程序完成。供电回路2只给最小系统供电,并不给耗电量大的外围部件供电。这样,给最小系统的供电时间足够长,可以完成敏感数据的保护操作。

通过软件测算,电容放电可供最小系统工作时间在0.5~4.5S之间。这种测算方法很简单.编写一个掉电中断服务子程序,这个程序只是不断进行时间刷新操作。同样,可以通过软件测定在这段时间里向Flash擦写2~3MB。可见,在采用这种硬件体制的情况下,系统掉电保护能够得到可靠的保证。

IEEE(国际电气和电子工程师协会)对嵌入式系统的定义:“用于控制、监视或者辅助操作机器和设备的装置”。原文为:Devices Used to Control,Monitor or Assist the Operation of Equipment,Machinery or Plants)。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。