利用低压晶体管进行高压电流检测

出处:维库电子市场网 发布于:2024-09-19 16:55:58 | 459 次阅读

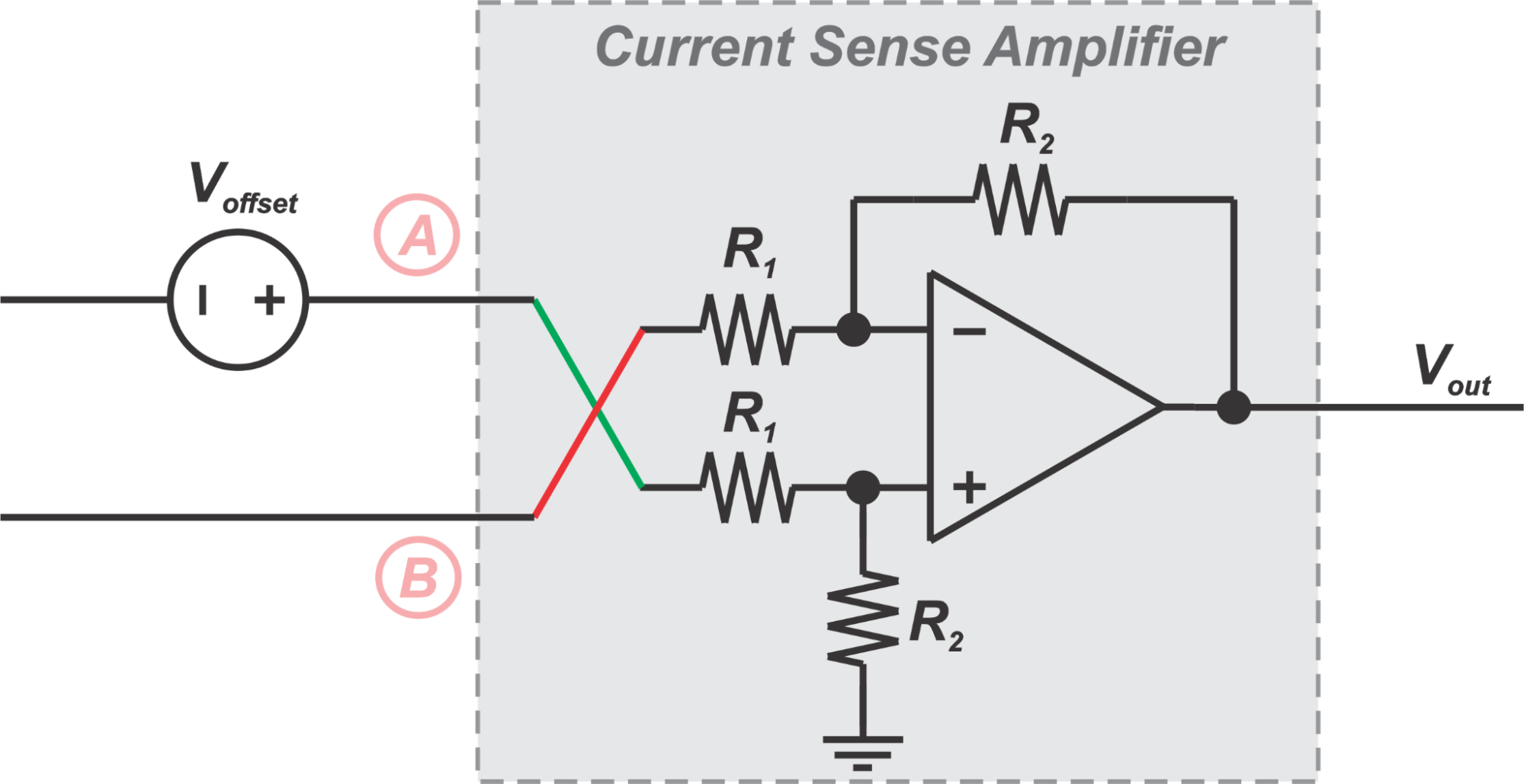

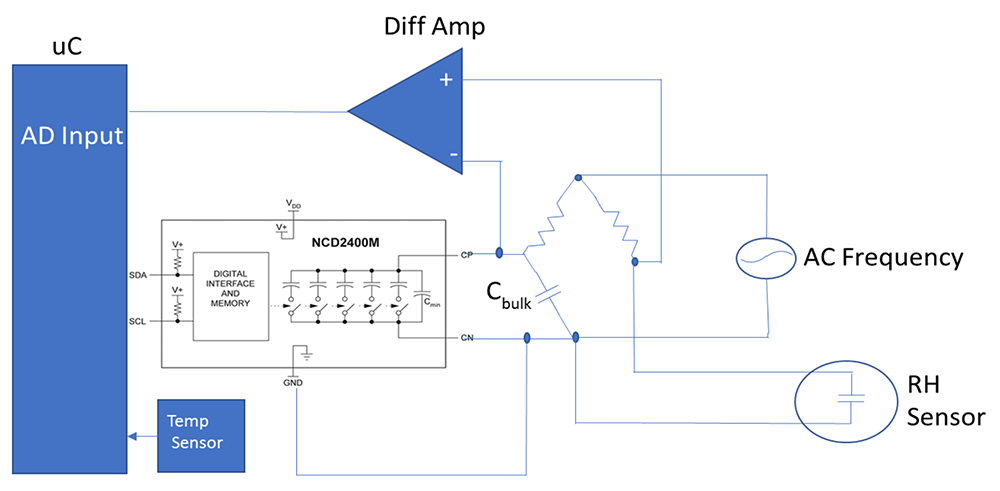

这种电路以及所有使用这种拓扑的电路的灵感源自电流镜拓扑和以下概念:Rsense 中的变化电流以及因此 Rsense 两端的电压会以线性方式改变 Re2 中的电流以及因此 Rc1 两端的电压。

图 1 中的电路的实用性归功于 Re1 和 Re2。使 Ireffairy 非常小,使 Re2 和 Re1 非常大且值相等,可增加发射极电压相对于 Rsense 两端电压的相对值。这反过来又降低了当负载在无负载和满负载之间变化时输出器件的 Vce 的变化。

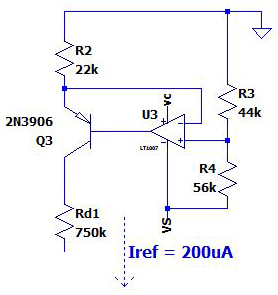

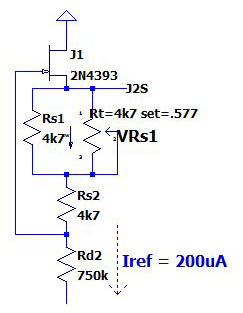

因此,通过合理选择 Iref、Re1、Re2、Rc2 和 Rc1,可以防止 Q2 进入饱和状态,同时不会超过晶体管的最大工作电压。请记住,hoe=I(集电极)/VA (早期电压)意味着减少 Icals 的变化会减少 β 的变化,从而改善线性度。Rc是 Rc1 和 Rc2 的总和,因此 Rc1/Rc 比率决定了无负载时 Vout? 处的偏移量。满载时 Rsense 上产生的电压决定了 Re2 和 Rc1 中电流的变化,因此决定了 Vout? 处的满量程输出。一旦确定了 Iref 的值,计算 Rc 和 Rd 上所需的无负载电压就很简单了。通过使用发射极电阻,变化的 Vce 对 Q2 的 β 的影响显著降低,并且检查模拟数据表明 β 的变化对负载电流和输出电压之间的相关性的影响相对较小。从所获得的结果来看,使用类似于威尔逊电流镜的配置可能是不必要的。 图 2 和图 3显示了恒流源产生 Iref 的替代方案。如果 Vss 稳定且无纹波,则可以省略恒流发生器,并可以选择 Rd 的值来提供 Iref。

图2恒流源产生Iref的替代方案。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。