基于Verilog HDL的I2C总线分析器

出处:chunyang 发布于:2009-10-26 16:42:11

要:提出了采用 Verilog HDL设计I 2C总线分析器的方法,该 I 2C总线分析器支持三种不同的工作模式:被动、主机和从机模式,并提供了嵌入式系统设计接口。通过硬件总体框架分析,分模块输入,经过仿真、逻辑综合和 FPGA硬件验证表明,该总线分析器与其它常用接口方式相比具有低功耗、占用资源少和功能完备等特点,并较少占用微处理器指令周期,应用在医疗检测系统中解决了增加可靠扩展平台问题。

1 引言

在医疗保健、临床医学和医疗救护中,血氧、心电、血压、呼吸、脑电波等生理信号都是非常重要的指标。针对临床应用,已经报道了将血氧、血压等检测应用于咽喉、食管等体内循环 [1],提高了准确性和及时性[2],这种方法正处在研究阶段,I 2C总线分析仪可以扩展医疗监测仪实现包括体外循环的多种方法同时检测和比较。现在医疗仪器短缺,一台带 I 2C扩展接口的监测仪可实现多人同时使用,资源得到有效利用。可见,实时、准确记录各项人体基本体征参数,同时具有便携式特点的医疗监测仪对健康监护、检测技术和医学研究具有重大意义。如何扩展医疗检测仪的功能成为热点问题。

目前扩展检测仪接口的方法很多,多通道是常用的方法,具有数据通道相对独立,有很强的抗干扰能力和设计复杂度优势,但体积较大,资源浪费多,不适合便携式处理。I 2C总线是一个工业标准同步串行数据通讯总线,被广泛应用在消费类电子和嵌入式系统产品中 [3],例如:数据转换器、EEPROM、传感器等等。相比现今流行的并口、SPI、USB等接口,虽然 I 2C有相对较低的带宽 [4],但功能多样化,广泛应用于信号处理器的控制接口设计。而且血氧饱和度有效信号基频在 1Hz左右,血压、呼吸、脑电波等生理信号的基频几十赫兹范围内。多种信号同时采集完全可以实现。同时应用I2C总线还有以下优点:一是各部分电路之间的连接变得非常简单,省去控制系统中的许多输入/输出接口,可靠性好;二是由于 I 2C总线具有多种工作模式,利用软件可以十分方便进行调整和测试,增加功能;三是 I 2C总线具有良好的扩展性,支持多主机通讯 [5]。本文描述了采用 Verilog HDL语言设计一种 I 2C总线分析器的硬件电路结构和它们主要特点,采用此设计可以实现多种传感器信号采集,方便实现与微处理器的接口设计,可重用性好,可以作为 IP核使用。

2 I2C总线标准模式

I2C总线是一种仅用到两线的工业标准同步串行数据通讯总线。两个总线:串行数据(SDA)线和串行时(SCL)线,对于嵌入式系统有限的 IO接口资源是非常重要的。I 2C总线支持从机、主机和多主机。每个I 2C器件有的识别地址(7位或 10位的地址)。串行的 8位双向数据传输传输有三种模式:标准模式(100kbits/s)、快模式(400kbits/s)、高速模式(3.4Mbits/s)。

I2C总线数据传输以字节为单位,按照高位在前顺序传输。数据传输首先以 I 2C主机发出开始条件和从机地址,读写控制字。从机必须对地址完成识别,之后传输由器件规则和协议定义的一系列读或写的数据。字节传输要有响应信号,确认后再发下一个字节,当通讯结束后,主机产生停止状态。

接收端采用SCL信号同步采样读取数据信息。I 2C协议规定数据变化只发生在 SCL信号为低电平期间,高电平期间要保持数据信号的稳定性。SCL信号线高电平期间,SDA信号由高电平变为低电平是开始条件,反之为停止条件。

3 硬件设计

I2C总线分析器为医疗检测仪或其它嵌入式系统提供很好的外设扩展。在不同工作模式下提供系统更多的功能。

在被动模式下,分析器探测总线上数据,传输数据或做算法处理。这里将采集到的数据直接通过 LCD显示,不占用微处理器资源;在主机模式下,分析器掌控总线,完成对外设的操作,如配置传感器,采集传感器信号;在从机模式下,分析器作为 I 2C器件使用,在被总线上主机识别后,接收或发送用户信息。

图 1显示了 I 2C总线分析器的硬件框图。采用 Verilog HDL语言描述,主要实现工作模式识别和I2C总线控制逻辑。采用层次化设计方法。硬件验证在 FPGA上实现。

3.1 控制信息模块和 I 2C状态机

这是 I 2C总线分析器和外部控制系统交换控制逻辑和状态信息的接口,决定着整个系统的功能。 I2C控制信息模块和状态模块产生总线上开始和结束状态请求,检测和总线信息(起始、停止、总线响应),产生 SCL脉冲信号,传输数据到SDA,控制两个FIFO(读和写存储器)。在模块中定义两个寄存器(系统控制寄存器 SYS_CONTROL和系统状态寄存器SYS_STAT)。

在控制寄存器中,位是初始化标识位,使系统进入等待状态;第 7位用于控制 I 2C总线产生起始状态;第 6位用于控制总线产生停止状态;第 5位控制读、写 FIFO存储器,低电平定义使用FIFO读存储器,高电平定义使用 FIFO写存储器;第 3、4位用于总线工作模式选择;第 2位用于主、从模式选择;一位作为总线传输响应。

状态寄存器反映工作状态。功能描述如下:位选择主、从机模式,第 7位标识总线状态,第 6、3位标识 FIFO存储器状态,第 5位标识数据通讯方向,第 4位为中断位,两位标识工作模式检测模式,共 8位。

3.2状态的产生和探测模块

根据协议,主机在 SCL高电平期间,在 SDA线上产生由 0到 1或由 1到 0的变化,前者代表开始条件,后者代表了停止条件。设计基于分频器完成,由控制信息模块可以产生所需 SCL信号,由 SCL信号倍频信号控制在 SCL信号高电平时产生 SDA信号。

在从机状态下,因为起始、停止条件是由 SDA在 SCL高电平期间改变来产生,所以设计中考虑用 SCL频率的 30、25或 16倍频来探测(高速模式下 56MHz可以由 PLL产生)。考虑在不同模式下采用不同倍频系数,虽然增加了设计复杂度和硬件的消耗,但从机能更地探测到起始和停止条件,提高系统性能。

3.3信息收集模块

系统作为从机,用系统时钟检测 SCL信号,确定主机的工作模式,并反映到状态寄存器。总线分析器由状态位产生相应采样时钟,在起始条件后采样主机发送的 7位从机地址、数据方向位(R/W)以及响应信息。

3.4器件地址模块

根据协议,每个 I2C器件都有独立地址。本设计有自定义 7位地址。如果信息收集模块中采样到地址与本地址一致,则作为从机操作。

3.5 FIFO读、写存储器

本设计中集成了两个 16×8的 FIFO,分别作为读、写存储器完成外部系统和 I2C总线数据传输。通过状态标志来控制产生中断,完成握手协议。如当接收 FIFO(读存储器)写满时,而外部系统端没有及时读走数据,如果继续从 I2C总线读取数据,就会丢失数据。通过 FULL标志,控制 I2C总线不产生响应,使之处于等待状态,直到系统读走数据。 FIFO硬件设计通过调用可编程器件内部存储器单元实现。

3.7 主系统状态机

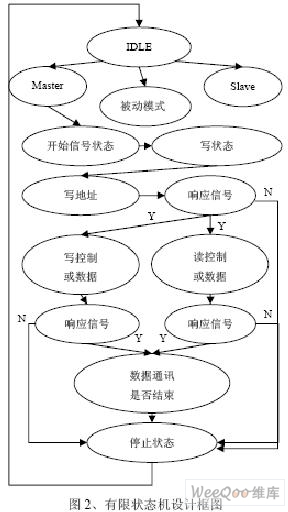

这是 I2C总线分析器的单元,需要完成在被动模式、主机模式和从机模式下状态转换和控制,根据控制寄存器中控制字,采用有限状态机嵌套设计完成。状态机编码采用独热编码,有利于提高传输速度并节省面积。

I2C总线分析器状态转移如图 2所示,整个过程受控制字和状态寄存器调节。图中主要描述了作为主机模式下状态变换,从机模式下,在准备阶段需要加上 I2C总线识别、器件地址识别,其它过程与主机相似,这里不详细描述。

下面以控制 VGA视频采集芯片 TMS8083为例说明:通过写 0x80h到控制寄存器来初始化系统;接着写入 0x92h作准备工作,进入主机状态、采用标准模式传输数据、对总线进行写数据、数据传输响应位:0;系统将要发送到总线的数据先写入 FIFO写存储器。 VGA采集系统采用 1024×768 at 60Hz → fpix=65.0MHz,N=1344模式,芯片地址和状态控制寄存器配置如下: 0x80h(器件地址和写状态标识)、0x00h(子地址)、0x40h、0x05h、0xeah、0xffh、0x90h、0xe1h、0x00h、0x03h、0x01h;将以上数据写入 FIFO后,向控制寄存器写入 0xd2h实现总线上起始条件;随后进入数据的传输阶段;数据传输完成,写 0xb2h到控制寄存器在总线上产生停止条件。

另外,采用移位寄存器完成数据接收和发送模块设计,,由顶层完成各模块时序控制,重点在于时钟信号管理,以达到同步目的。

4 验证

采用 Verilog HDL语言完成设计输入,用仿真工具在硬件编程前验证设计,综合编程后用逻辑分析仪检验硬件功能。QuartusII工具提供了完成设计开发平台

4.1

仿真 I2C总线分析器主要有主机写操作、读操作和作为从机写操作、读操作功能。采用 Verilog HDL语言建立测试平台,联合 ModelSim完成功能和时序验证。

图 3波形验证了主机向从机发送地址和写数据的过程:发送 7位地址 0x40h和写控制字0,即0x80h、8位数据 0xa8h。在 I 2C总线上,首先产生起始条件,接着发送从机地址和写控制信号,采样响应信号后再发送数据,响应后产生停止条件。由下图的波形分析,主机能正确的发送地址和数据,应对从机响应。

下面测试作为从机接收数据,检测I 2C总线信息,探测起始条件,接收从机地址和R/W,地址不同无响应,地址相同产生响应信号,并开始接收数据。I 2C总线分析器的地址定义为0x50h。仿真波形如图 4所示。由上图的波形说明设计能够很好完成作为从机的功能。

4.2 硬件验证

采用 Altera Cyclone器件 EP1C12验证硬件。通过编程,调用 SignalTapII Logic Analyzer工具,实时观察设计的内部信号波形。

图 5显示了由逻辑分析仪得到的结果。I 2C总线分析器作为主机很明显能够驱动总线,向从机发送从机地址、命令和数据,符合对 TMS8083应用中传输数据描述,能进行正确通讯。

5 总结

本文作者创新点:提出了一种新的应用于医疗监护仪扩展接口的 I 2C总线分析器,具有低功耗、便携式特点。能够很好地连接微控制器及其外围设备,满足具有可扩展功能的需求,适合于开发便携式设备。在开发具有可扩展功能的便携医疗监护仪嵌入式项目中仅需要设计相应系统软件库,即可将 I 2C总线接口扩展到桌面系统应用中。I 2C总线在少的硬件资源消耗下将为项目带来更多的拓展空间。同时经过综合后仅占用 EP1C12器件的6%逻辑单元,可以进一步提出了新的基于 NIOSII开发便携医疗监护仪思想,必将大大缩小体积,提高系统可靠性。

参考文献:

[1]. VGA datasheet https://www.dzsc.com/datasheet/VGA_2568786.html.

[2]. Altera Cyclone datasheet https://www.dzsc.com/datasheet/Altera+Cyclone_2445471.html.

[3]. EP1C12 datasheet https://www.dzsc.com/datasheet/EP1C12_527237.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PLC 编程中急停开关触点抉择:常开还是常闭?接线要点揭秘2025/6/26 16:02:37

- 全面解析:PLC 控制柜设计原理、布局接线与原理图2025/6/16 16:12:05

- PLC控制系统输入/输出回路的隔离技术2025/6/12 17:27:11

- 深度解析:PLC 上升沿和下降沿指令的应用时机与使用方法2025/6/9 15:18:19

- 利用 PLC 轻松打造红绿交通灯控制系统2025/5/29 15:36:55