基于PLC的SD加法器在DSP领域中的应用

出处:何召兰 袁丽英 徐倩 发布于:2007-09-26 17:07:26

关键词:PLDSD数表示 SD加法器 DSP

信息社会的标志性产品是电子产品,现代电子产品的性能越来越高,复杂度越来越大。在当今信息时代,数字技术已成主流。数字信号处理技术(DSP)在许多领域内具有广泛的用途,如雷达、图象处理、数据压缩和数字通信机等。传统的解决数字信号系统设计问题的方法主要有两种:(1)采用DSP处理器,(2)采用固定功能的DSP器件或ASIC器件。随着DSP系统复杂程序和功能要求的提高,这些DSP解决方案暴露出缺陷。DSP处理器方案成本低,但处理数据的实时性能差,限制了它在高速和实时系统中的应用;固定功能的DAP器件或ASIC器件可提供良好的实时性,但其灵活性差,不适合在实验室或技术开发等场和使用。现在,大规模可编程逻辑器件为DSP提供了第三种方案,CPLD及FPGA和DSP技术结合,能够在集成度、速度和系统功能方面满足DSP的需要,同时具备DSP处理器的灵活性和固定功能DSP芯片的实时性[2]。

加法器和乘法器是构成所有DSP系统的基本结构。加法器是基本的DSP算法,无论乘法、减法、除法或FFT运算终也要分解为加法运算。应用传统的二进制数表示实现的许多超大规模集成运算电路可完成大量数据的实时运算,但进位限制了运算速度[3]。因此,一个没有进位的求和运算系统是众所期望的。

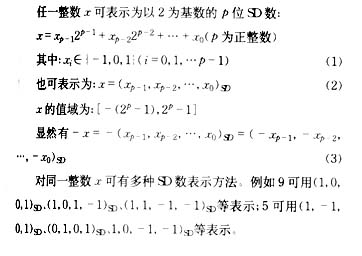

SD数是一种性能优良的数值表示形式[4],在运算过程中可限制进位的产生,且位数的增加不影响运算速度,实现了真正意义上的并行运算。在本文中我们提出了一种新型的基于以2为基数p位SD数表示的加法电路。以下给出了SD数的表示方法,并用SD数在可编程逻辑器件[2]上用硬件描述语言(VHLD)实现SD加法器。

1 以2为基数的SD数表示方法

2 用SD数表示的求和算法

应用以上SD数表示方法,无需进位即可实现加法运算。而通常以二进制数表示的加法运算过程中都要产生因为,位数越多产生的进位越多,将严重影响运算速度[1]。两个p位SD数相加,即s=a+b,可通过以下两步实现。

设ci、mi和si分别是第i位SD数(i=0,1,2,…,p-1)的中间进位、中间和及结果,每一位都按以下两个步骤进行计算。

p=5时,a=(1,0,-1,-1,-1)SD=9,b=(1,-1,0,-1,-1)SD=5,图1说明了不同p值的SD数表示的5+9=14的计算过程。

由图1可知,应用以上算法实现的求和过程只需两步即可完成,且运算速度与操作数位数无关。而传统的二进制数求和运算则有进位产生,并行进位加法器结构简单,但产生的进位信号逐级传递,降低了运算速度,操作数位数越多,运算速度越慢;超前进位加法器可缩短运算进间,但增加了电路复杂程度,当加法器位数增加时电路的复杂程度随之急剧上升[1]。SD加法器可克服其缺点。

3 用VHLD实现SD加法器

根据SD数求和算法基础上,图2给出了SD加法器的方框图。一个p位SD加法器由p个基本运算单元SD全加器(SDFA)组成,每一个SDFA包含ADD1和ADD2,ADD1执行上述算法中的步,ADD2执行第二步。SDFA的逻辑电路可用VHDL实现。

VHDL是一种全方位的硬件描述语言,包括从系统到电路的所有设计层次[6]。在描述风格上VHDL支持结构、数据流行和行为3种描述形式的混合描述,几乎覆盖了以往各种语句描述语言的功能。整个自顶向下或自底向上的电路设计过程都可以用VHDL来完成[5]。本文应用HVDL设计以上提出的SD求和算法电路-SD加法器。

表1中规定了以2为基数SD数ai的二进制表示方法,其中ai(1)是ai的符号,ai(0)是ai的绝地值。因此,以2为基数的p位SD数可由2p维向量表示:

图2说明了上述算法所描述的SD数求和过程。现在考虑基本运算单元SDFA,每一个SDFA中的ADD1都有8个二进制输入信号,可通过改变式(6)、(7)的条件减少输入信号。

OR是逻辑或运算符,上式中由于abs(ai)≠abs(bi),所以T=1时,(ai+bi)=-1,TL=1时(ai-1+bi-1+bi-1∈{-1,0},条件的变化仍能确保mi和ci-1符号不同,si∈{-1,0,1},因此ADD1的输入信号由8个减少到6个,简化了逻辑电路。根据以上描述的输入、输出信号之间的逻辑关系即可用VHDL在PLD上设计出SDFA的逻辑图[2][5]。

4 结论

本文提出的SD数表示方法,值域宽,表示灵活方便,基于SD数的求和算法速度高、电路简单,运算速度不受进位和操作数位数的限制,可实现高速求和运算。DSP系统中的数值计算和数据处理都是在求和运算基础上实现的,求和运算的速度直接影响整个系统的运行速度。因此,本文用VHDL在PLD上实现的SD加法器可同时满足DSP系统对灵活性和实时性的要求,在DSP领域中具有重要的实用价值。

参考文献:

[1]. CPLD datasheet https://www.dzsc.com/datasheet/CPLD_1136600.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 单片机技术特性与嵌入式开发实践指南2026/1/7 10:00:02

- 单片机(MCU)与数字信号处理器(DSP)分类及选型技术指南2025/12/30 10:02:37

- 工业级DSP信号处理系统:硬件适配与抗干扰工程方案2025/12/15 14:41:00

- HOLTEK推出HT32F65533G/733G内建N/N预驱电机专用SoC单片机2025/11/26 14:11:41

- 什么是C51数据类型扩充定义2025/10/27 13:59:22