基于FPGA的LCD%26amp;VGA控制器设计

出处:z1y2u3 发布于:2007-09-29 09:52:33

1 图形显示系统简介

图1是飞机座舱图形显示系统结构框图。图中处理器采用AD公司的ADSP21061芯片,AMLCD采用Korry公司的KDM710全彩色液晶显示模块,该模块为5%26;#215;5英寸、600%26;#215;600分辨率彩色液

|

|

2 KMD710显示模块

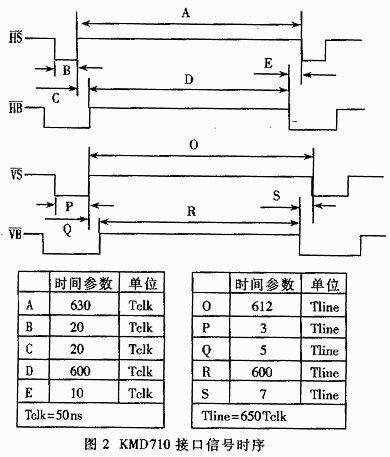

如图1所示,美国Korry公司提供的KDM710全彩色液晶显示模块接口信号主要如下几组:3个8位RGB数字信号、行同步信号HSYNC、场同步信号VSYNC、数据使能信号DATA_EN和点时钟输入DCLK。根据AMLCD数据手册所需求的时序,确定扫描时序和相应的时序参数如图2所示。一般,图形终端显示器扫描制式与广播电视的标准有点不同,须根据显示模块所提供的时间要求来确定扫描时序,其中的行场同步的前后肩,可以根据需要进行微调,一般为了防止每行的个象素丢失,要求行同步后肩C与行同步脉冲宽B尽量相等。图2中的点时钟为20MHz,行周期为650个时钟周期,场周期为615个行周期(场频为50Hz)。

3 LCD%26;amp;VGA控制器设计

设计行场扫描时序,一般有两种方式:查找表方式和编程逻辑方式。查找表方式主要由存储芯片构成,如SRAM、EPROM、PORM等。使用时,先根据所要产生的时序在存储单元写入相应的数值,查表时再从表内读出时应存储单元的数值,以形成扫描时序。扫描时序查找表分为行扫描时序查找表和场扫描时序查找表。场扫描时序查找表的输入时钟由行同步脉冲提供。用查找表形成时序的方法存在体积大、计算烦琐的缺点。随着大规模逻辑芯片的出现,利用编程逻辑方法产生行场扫描时序是一个发展方向。这种方法具有电路简单、功能强、修改方便、可靠性高等优点。图3为LCD控制器的框图。

在本设计中,点时钟DCLK由处理器DSP的系统时钟40MHz经数字锁相环二分频得到。点时钟驱动行时序生成器,产生图2所示的行同步信号HS和行消隐信号HB。为避免毛刺,控制器设计采用同步设计方法,如图3所示,行同步信号HS通过一个微分电路,产生一个点时钟周期宽的场时序生成器使能信号。在使能信号有效时,场时序生成器开始计数,并产生场同步信号VS和场消隐信号VB。行消隐信号HB和场消隐信号VB相与后即为数据使能信号DATA_EN。该数据使能信号作为产生帧存地址计数器的计数使能,以保证DATA_EN信号为高时,将象素送给AMLCD显示。在DCLK的上升沿,帧存地址计数器加一,帧存SRAM经过一段延时后,象素数据出现在总线上。在DCLK的下降沿AMLCD将数据读入。该LCD控制器的设计方法很容易用于VGA视频接口。在VGA接口电路的设计中,不需点时钟电路,只须将行同步信号与场同步信号输出,将数据使能信号作为复合消隐信号输入即可。产生行场扫描时序的VHDL描述如下:

entity seq_gen is port(clk_seq : in std_logic; rst_seq : in std_logic; LCD_hs_out : out std_logic; lcd_dataen : out std_logic; lcd_vs_out : out std_logic; pix_clk : out std_logic ); end seq_gen; architecture rtl_seq_gen of seq_gen is signa

l lcd_hb : std_logic; signal lcd_hs : std_logic; signal lcd_vb : std_logic; signal lcd_vs : std_logic; signal clken_vcount : std_logic; begin hcount: block signal hcountreg :std_logic_vector(9 downto 0); signal hz_temp : std_logic; signal lcd_hz : std_logic; begin process (clk_seq,lcd_hz) begin if (lcd_hz = "1") then hcountreg <= (others =>"0"); elsif clk_seq"event and clk_seq = "1" then hcountreg <= hcountreg +1; end if; end process; lcd_hb <= "0" when hcountreg >=600 and hcount

|

|

reg < 650 else "1"; lcd_hs <="0" when hcountreg >=610 and hcountreg < 630 else "1"; hz_temp <= "1" when hcountreg = 650 else "0"; lcd_hz <=hz_temp or rst_seq; end block hcount; diff : block signal inputrega : std_logic; signal inputregb : std_logic; begin process(clk_seq) begin if clk_seq"event and clk_seq="1" then inputregb <= inputrega; inputrega <= not lcd_hs; end if; end process; clken_vcount <= not inputregb and inputrega; end block diff; vcount : block signal vcountreg : std_logic_vector(9 downto 0); signal vz_temp : std_logic; signal lcd_vz : std_logic; begin process (clk_seq,lcd_vz) begin if(lcd_vz="1")then vcountreg <= (others => "0"); elsif clk_seq"event and clk_seq = "1" then if clken_vcount = "1" then vcountreg <= vcountreg +1; end if; end if; end process; lcd_vb <= "0" when vcountreg >=600 and vcountreg < 615 else "1"; lcd_vs <="0" when vcountreg >=607 and vcounreg < 610 else "1"; vz_temp <= "1" when vcountreg = 615 else "0"; lcd_vz <= vz_temp or rst_seq; end block vcount; pix_clk <=clk_seq; lcd_dataen <=lcd_hb and lcd_vb; lcd_hs_out <=lcd_hs; lcd_vs_out <=lcd_vs; end rtl_seq_gen; 这种用VHDL产生扫描时序的方法简单、易读,并且易于修改。在代码中只须修改一些时序参数就能产生任意时序的波形,具有很好的可重用性。

采用FPGA技术设计的AMLCD控制器,大大减少了电路板的尺寸,同时增加了系统可靠性和设计灵活性。这种用VHDL语言实现现行场扫描时序生成器的方法,具有简便。易读和可重用性强的特点。该AMLCD控制器已用Xilinx公司的SpartanII系列器件XC2S50实现,并在飞机座舱图形显示系统中实现应用。

(朱耀东 经亚枝 张焕春 )

参考文献:

[1]. VGA datasheet https://www.dzsc.com/datasheet/VGA_2568786.html.

[2]. EPROM datasheet https://www.dzsc.com/datasheet/EPROM_1128137.html.

[3]. XC2S50 datasheet https://www.dzsc.com/datasheet/XC2S50_1096648.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- LED照明技术特性与选型运维指南2026/1/5 10:26:27

- 工业触摸屏选型与现场应用技术指南2025/12/22 11:44:57

- 显示器色深 6Bit、8Bit、10Bit 与 6 抖 8、8 抖 10、FRC2025/8/28 15:29:32

- Micro-LED技术解析2025/8/26 17:21:56

- LED显示屏标清、高清、超清、1080P与4K的解析2025/8/8 17:05:00