基于PC104总线的2FSK调制器的设计与实现

出处:gdstcwl 发布于:2010-03-01 16:48:41

嵌入式计算机系统在现代工业控制中发挥着越来越重要的作用,它具有便携、可靠、低功耗、通用、易扩展等诸多优点。使用嵌入式系统进行工业控制要涉及到计算机数据的传输、采集、调制解调等一系列问题。

本调制器是一种基于PC104总线的嵌入式系统的外围设备,嵌入式计算机系统通过PC104总线将数据发送到端口,调制器接收数据并进行调制后,将信号输出到受控设备,从而对相应设备起到控制的功能。在本调制器的硬件电路中使用FPGA,提高了系统的通用性。

1总体结构

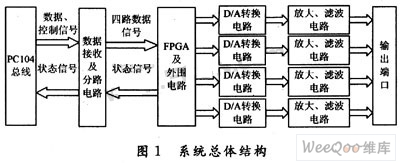

该调制器实现的功能主要包括:识别并接收总线发送的数据;根据不同地址控制信号将数据按路区分(共四路);每路分别将数据按照连续调制的方式进行2FSK调制;对调制后的信号进行放大整形并发送到端口。

因此,该调制器的电路部分分别包括数据接收部分、FPGA及外围电路(实现数据分路及数字调制功能)、D/A转换电路、放大滤波电路等。系统总体结构如图1所示。

2 PC104总线及数据接收电路

PC104总线是专门为嵌入式系统开发的系统总线,是一种自堆栈式、模块化的总线,它基于ISA总线发展而来,有16位和8位两种接口方式(分别为64+40引脚和64引脚端口结构),该总线具有结构紧凑、便携、可靠、功耗低、易扩展等优点。对于工程开发而言,常用的引脚主要有以下几个:

SD0~SD7,SD8~SD15:数据总线,当采用8位接口方式时,只有SD0~SD7工作;

SA0~SA19,LA17~LA23:地址信号,对端口进行操作时使用SA0~SA9;

AEN:DMA选通信号,为高电平时表示处于DMA模式;

IOW,IOR:端口写、读信号,低电平有效;

SYSCLK:系统提供的基准时钟信号,是标准的方波信号,约为8 MHz;

VCC,GND,+12 V,-12 V:系统提供的电源接口。

数据接收电路就是要在正确的时序上将所需的数据进行提取,还要实现将电路工作状态传送回总线,以便总线决定是否发送下组数据的功能。由于PC104总线支持约8 MHz的时钟频率,而受控设备所需的2FSK信号频率为几千赫兹,因此这里只用8位数据总线就完够满足要求。

总线接收电路如图2所示。其中SD0~SD9,SA0~SA9是从总线发来的数据、地址信号,SEL0~SEL3为分路选择信号,ANSWER0~ANSWER3为FPGA的状态返回信号,由于总线速度要比2FSK输出速度高得多,因此,总线要对FPGA数据缓存器是否为空进行查询,当FPGA没有完成数据转换时,总线要等下个周期,直到状态返回信号显示FPGA内部为空时,总线才可以发送下组数据到FPGA。74LS273负责将每路的数据分别进行锁存,4路数据共使用4个。OUT1D0~D7为路8位数据输出,LOCK0为其控制信号,表示数据的更新。

3 FPGA及其外围电路

FPGA具有集成度高、设计灵活、易于修改、节省空间、通用性高等优点。本调制器中FPGA采用的是Altera公司的EPF10K20TC144-4器件,该器件具有20 000个典型门,1 153个逻辑单元,144引脚,包括2个全局输入时钟,4个全局输入,86个通用可编程I/O引脚。该芯片采用TQFP封装,芯片面积较小,功耗低,其输入、输出与TTL,与PC104总线电平完全兼容。FPGA电路主要实现的功能为:接收数据提取电路发送的分路数据;以总线上的SYSCLK时钟为基准,通过分频产生受控设备能识别的频率;为每路输出进行2FSK的数字调制,保证信号的连续性;完成本身的FPGA电路配置。

FPGA配置电路如图3所示。

FPGA的配置使用PS和JTAG两种方式,既能实现JTAG方式下电路在线调试,又能保证调试完成后能够正确使用相应的配置器件。其中JP5*2插座为JTAG配置端口,TDI、TDO、TMS、TCK为JTAG配置引脚,该配置方式采用BlasterMV线,通过配置计算机的并口与电路板配置端口进行连接,用于将编写好的配置数据实时传送到FPGA,该方式主要用于电路调试;EPC1PC8为FPGA配置器件,采用PS(被动串行)配置方式,由于FPGA内部存储器属于易失性RAM存储,因此每次加电后都要将程序重新写入FPGA,配置器件本身就是存储器,其主要作用就是在每次加电后将程序写入FPGA,保证调试完毕的电路能够正常单独进行工作。

来自前级电路的数据及控制信号、发到D/A转换电路的数据都连接到FPGA芯片的通用I/O引脚,通过编程实现所需功能。对FPGA的编程使用Altera公司的QuartusⅡ软件,该软件采用图形化与VHDL语言混合编程,易于调试修改。编程实现的主要功能为:对输入数据进行锁存移位,确保每位数据都能得到正确处理;产生两组分频时钟参与2FSK调制,并使分频后的时钟按照时序进入数字调制器;数字调制器负责将不同频率始终按照顺序依次产生连续量化的8位正弦波数字量输出到端口。

本设计中由于采用两种频率分时产生,按时序进入调制器,而正弦波数字调制器单独工作的方法,保证了输出正弦波具有连续的相位,不会产生相位突变。

4 D/A转换电路

D/A转换共包括四路,其主要功能是将FPGA输出的已调制好的2FSK数字信号转换为正弦波信号。由于FPGA在进行数字调制时产生的是连续量化的正弦波形,两个频率之间不存在相位的突变,不会存在大量的高频杂波,因此,后期的信号处理电路使用放大电路与简单的π型滤波器对信号进行处理即可得到比较理想的2FSK信号。

D/A转换电路如图4所示。

此电路采用AD7524作为D/A转换器,AD7524属于T型电阻网络型DAC,电流输出,8位数字输入,输出建立时间0.2μs/0.15μs,其数字输入端可采用5 V/15 V两种输入,本电路采用兼容TTL电平的5 V输入。电路中将其输入控制端CS、WR同时接地,当有来自FPGA的数据AD101~7输入时无需锁存,直接进行转换,因此要求FPGA的输出要具有锁存功能,此接法可减少输出控制线,减少时序干扰。R1AD1和R1AD2为D/A输出波形调整电阻,主要用于调整波形位置,不致产生失真。D/A输出采用双极性接法,通过两路LM324通用放大器进行电压放大,输出2FSK信号。图5(a)为经过D/A转换后输出的波形在示波器上的截图,由图中可以看到,数字调制并经D/A转换后,波形是一种阶梯状正弦波,且波形连续,频率变换交界处无相位突变。该信号经过双极性放大器放大并通过π型滤波器后变成如图5(b)所示的连续正弦波。

5结语

采用FPGA进行2FSK调制不但能产生连续相位,还能通过软件直接修改其调制方式、产生频率等一系列参数,具有很好的通用性。

本电路中数据提取电路属于原理性电路,实际设计中可将该部分电路置于FPGA内部进行设计,而系统参考时钟SYSCLK可接在FPGA的全局时钟输入端,减少延迟差异。

参考文献:

[1]. LA17 datasheet https://www.dzsc.com/datasheet/LA17_444854.html.

[2]. 74LS273 datasheet https://www.dzsc.com/datasheet/74LS273_588907.html.

[3]. TQFP datasheet https://www.dzsc.com/datasheet/TQFP_1528902.html.

[4]. TTL datasheet https://www.dzsc.com/datasheet/TTL_1174409.html.

[5]. EPC1PC8 datasheet https://www.dzsc.com/datasheet/EPC1PC8_1054146.html.

[6]. AD7524 datasheet https://www.dzsc.com/datasheet/AD7524_1055432.html.

[7]. AD101 datasheet https://www.dzsc.com/datasheet/AD101_121151.html.

[8]. LM324 datasheet https://www.dzsc.com/datasheet/LM324_1054816.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 深入解析嵌入式 OPENAMP 框架:开启异核通信新时代2025/7/22 16:27:29

- 一文快速了解OPENWRT基础知识2025/7/14 16:59:04

- 独立 ADC 优势大揭秘:为何不可替代?2025/7/7 16:21:04

- 深入剖析:嵌入式中 RS485、RS422 和 RS232 的特点差异2025/7/5 15:07:54

- 揭秘嵌入式 MCU:浮点数据处理难点及应对策略2025/6/20 15:19:07