CEVA发布首款针对可授权DSP的优化工具链

出处:EEWORLD 发布于:2011-06-02 12:19:59

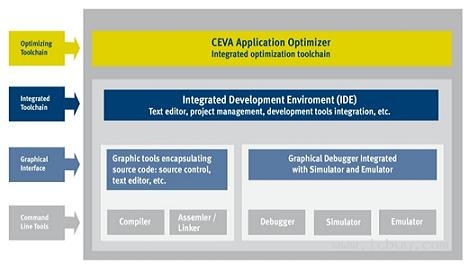

CEVA推出首款针对可授权DSP的基于C语言的应用程序优化工具链。该应用优化器 (Application Optimizer) 包括于CEVA-ToolBox 软件开发环境套件内供货,可以让应用开发人员完全以C语言级轻易开发CEVA DSP软件,不需要任何手写的汇编语言,显着提高了 SoC 设计的总体性能并缩短其设计周期。

较其它可授权解决方案具有显着的性能优势

加入了应用优化器后,CEVA DSP内核的开发环境获得显着增强,并可大大简化软件开发流程,提高目标应用程序的性能。以使用标准窄带自适应多速率压缩 (AMR-NB) 的C语言语音编码器为例,CEVA-X1622 DSP内核在编译现成可用的代码 (差帧幅及流) 时,仅需19 MHz速率;而其它的可授权解决方案却需要高45% 以上的速度,才能编译同样的现成代码。

*这些数字以差帧幅和流为基础,使用标准的ITC/3GPP C参考代码

** AMR-WB 使用8.85Kbps的比特率

大幅缩短软件开发时间

随着现代 SoC 架构设计的复杂性不断增加,嵌入式软件开发的重担给 IC 供应商带来了艰巨的挑战,针对特定多元化系统架构编写和优化软件的工作,成为了设计过程的瓶颈。利用应用优化器工具链,结合CEVA-ToolBox? 开发环境中的其它重要组件,能够把软件设计流程转到纯C语言,并可降低对设计工程师在专用架构方面的知识水平的要求。

据市场研究机构Forward Concepts公司总裁兼创始人Will Strauss表示:“由于当今芯片设计的高度集成化,加上这些先进处理器的编程复杂性不断提高,开发工具已成为DSP选择的关键考虑因素。针对CEVA DSP内核而增加的全面端到端C 语言级软件优化工具链,可为设计DSP应用程序的客户提供重要优势,避免冗长繁琐且费时的汇编级优化工作。”

应用优化器的主要组件包括:

◆ 项目建立优化器 (Project build optimizer):创建经优化的建立配置,根据客户应用与真实的系统条件,仿真和剖析多种应用场景

◆ DSP 及通信软件库:C可呼叫 (C-callable) 汇编的优化功能,大大提升DSP及通信应用的性能,并缩短开发时间

◆ 应用剖析器 (Application Profiler):一个周期的C语言级应用程序及存储器子系统剖析器

◆ 基于评分的编译:现成可用的C代码与经优化汇编的代码,二者比值小于1:1.5

应用优化器的其它重要组件还有:链接后 (post linker) 优化器、便于算法 (如MATLAB) 移植的调试器连接,以及测试环境自动控制。

开发工具和支持

CEVA的DSP内核备有强大的开发环境的支持,包括软件开发工具、开发板、软件系统驱动器和RTOS。这个开发环境是CEVA自1991年推出首款DSP内核以来,数千人一年工作量所累积之技术经验的结晶。CEVA的工具和技术支持已获世界各地数以千计的工程师使用,生产采用CEVA技术的芯片,至今为止付运了超过10亿片芯片。这些开发工具可以在Windows、Solaris 和 Linux操作系统上运行,并由世界各地的客户服务团队提供支持。此外,CEVA DSP内核还获得CEVA 和CEVAnet第三方开发团体提供的广泛的算法和应用支持。

关于 CEVA

CEVA公司总部位于美国加利福尼亚州圣何塞,是向移动手机、便携和消费电子市场提供硅知识产权 (SIP) DSP内核和平台解决方案的授权厂商。CEVA的IP系列包括面向多媒体、音频、分组语音 (VoP) 、蓝牙 (Bluetooth) 和串行 ATA (SATA) 的广泛全面的平台解决方案,以及各式各样的可编程 DSP 内核和针对多个市场的不同性价比子系统。2008年,CEVA 的 IP 在3亿多个系统设备上使用。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 掌握 DSP:原理剖析与应用实践2025/5/8 14:03:24

- 模糊逻辑在 DSP 上实时执行2023/7/25 17:13:30

- 多速率DSP及其在数模转换中的应用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系统的信号完整性2022/9/26 16:45:38