简述TMS320F2812与ARINC429数据总线之间的通信设计

出处:赵国辉,王小鹏,王 杰 兰州交通大学 发布于:2011-08-26 14:23:04

ARINC429总线广泛应用于商务运输航空领域,如空中客车A310/A320、A330/A340飞机,波音公司727、737、747、757和767飞机,麦道公司MD-11飞机等。它采用异步双极性归零码进行数据的编码,并通过双绞线传输,具有很强的抗干扰性能。目前市场上的ARINC429总线接口设计一般都采用专用接口芯片,如Device Engineering公司的DEI-1016,INTERSIL公司的HS-3282等,这些专用芯片价格昂贵,且路数有限,使用非常不灵活。为了使系统能够对ARINC429数据进行处理并将处理好的数据发送出去,文中提出了一种基于DSP和ARINC429专用协议芯片HS-3282的总线数据设计方法。

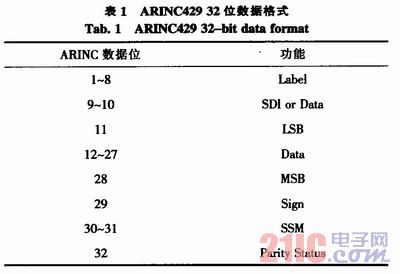

1 ARINC429数据传输规范

ARINC429数据总线协议规定一个数据字由32位组成,以脉冲形式发送,采用双极性归零码,码速率为12.5kb/s或100kb/s.电气特性为:高电平(+10V)为逻辑1;低电平(-10V)为逻辑0;0电平(0V)发送自身时钟脉冲,字与字之间以一定间隔(不少于4位)分开,以此间隔作为字同步。一个32位的数据字由五部分组成:标志位(LABEL),用于标识传输数据的信息类型;源/目的标识码(S/D),用于判断在一个多系统中的源系统;数据区(DATA);符号/状态位(SSM),用于标识数据字的特征或数据发生器的状态;奇偶校验位(PARITY),ARINC429数字信息传输使用奇校验。ARINC429数据格式如表1所示。

2 系统硬件设计

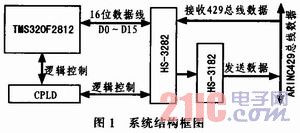

本系统主要是实现ARINC429总线数据信息的接收和发送。本系统中采用TI公司的DSP芯片TMS320F2812为控制和CPLD芯片作译码电路控制429数据收发芯片时序逻辑,配合1片高性能ARINC429数据收发芯片HS-3282和1片ARINC429数据发送驱动芯片HS-3182,形成1个数据接收通道和1个数据发送通道,由它们构成数据收发、串/并、并/串转换的主体,其系统结构框图如图1所示。

2.1 TMS320F2812

DSP2812功能比单片机强大的多,TMS320F2812 是美国TI 公司推出的C2000 平台上的定点32 位DSP 芯片,适合用于工业控制,电机控制等,用途广泛,应该相当于单片的升级版。运行时钟也快可达150MHz,处理性能可达150MIPS,每条指令周期6.67ns.IO口丰富,对用户一般的应用来说足够了。两个串口。具有12位的0~3.3v的AD转换等。具有片内128k×16位的片内FLASH,18K ×16 位的SRAM,一般的应用系统可以不要外扩存储器。具体的指标你可以查阅相关的数据文档。单片机电源是5v.dsp2812的内核1.8v供电,IO是3.3v供电。单片机有贴片或DIP,2812的引脚根据封装的不同有176脚的LQFP, 179脚的MicroStar BGA.

2.2 HS-3282简介

HS-3282是美国Harris公司生产的专门面对ARINC429总线的一种高性能CMOS总线接口芯片,能满足ARINCA29协议的译码、时分复用、串行数据协议等标准的要求。当它与驱动芯片HS-3182配合使用时,能正确收发ARINCA29规范数据,且抗干扰性能好。因而采用其来设计ARIN-C429总线接口电路既简单、有效,又能保证可靠性。

HS-3282包含两路接收器和一路发送器,接收器和发送器分别独立工作。两个分别独立的接收器直接与ARINC429总线相连,并以十倍于接收数据速率的频率工作,发送器的数据速率可以与接收器速率相同或不同。尽管两个接收器工作在同一个频率下,但是它们独立工作并异步接收串行数据。ARINC总线接口芯片发送器主要包括FIFO存储器和时钟电路。FIFO存储器能够为发送器连续保存8个ARlNC数据。时钟电路用来正确分隔每个ARINC数据字以满足ARINC429规范。尽管ARINC429规范指定为包含校验位的32位字,通过编程,HS-3282的数据字长度也可以为25位。HS-3282接收器是将串行429数据转换为2个并行的16位数据,而发送器则是将2个并行的16位数据转化为串行429数据。

2.3 ARINC数据收发模块

ARINC(美国爱瑞克)公司,全名为航空无线电通信公司Aeronautical Radio Inc.,成立于1929年12月2日,由当时的四家航空公司共同投资组建,被当时的联邦无线电管理委员会FRC(后更名为联邦通信管理委员会)授权负责"独立于政府之外协调管理和航空公司的无线电通信工作".公司初期的主要工作是按照FRC的规定建设和运行地基的航空话音通信设施和网络(高频HF工作方式),并为民航和军航提供HF话音通信服务。公司总部位于美国马里兰州安纳波利斯市,员工3100人,143办公室,分布102个国家。欧洲区总部位于伦敦,建立于1999年;亚太区总部设于新加坡,成立于2003年;中国总部设于北京。

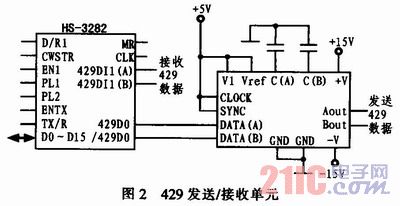

该模块主要完成ARINC429数据的接收、发送和速率转换等功能,利用1片高性能的ARINC429数据收发芯片HS-3282和1片ARINC429数据发送驱动芯片HS-3182完成一路接收和一路发送通道,由它们完成数据缓存,串/并、并/串转换和系统内部逻辑信号与ARINC429差分信号的转换。

HS-3182为正式差分输出,用来把要发送的信息转变为符合ARINC429传输规范的电平,与驱动芯片HS-3182相连的电容用来改善输出数据的上升沿和下降沿,这里对于不同的数据传输速率选择不同的电容,75 pF电容对应ARINC429总线高速工作状态,300 pF电容对应低速作状态,这两个电容极其重要,为了提高稳定性、降低干扰,采用军品电容。

数据发送单元主要完成把并行的信息转化为串行信息,再把串行信息转变为双极性归零码,发送至ARINC429总线。数据接收单元主要把ARINC429总线上来的双极性归零串行信息转变为一般的串行信息,再经过移位寄存器转换为并行信息。ARINC429数据发送/接收单元的原理图如图2所示。

HS-3282中D/R1接F2812的外部中断,使429数据接收为中断接收;CWSTR、ENTX、TX/R、MR等经电平转换连接到F2812的I/O口;429DI(A)和429DI(B)直接连接429总线,接收来自429总线的数据;429D0及/429D0和HS-3182的DATA(A)、DATA(B)连接,将HS-3282发送器的数据经HS-3182驱动后发送至429总线。

2.4 CPLD逻辑控制

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计。

对于F2812,每个区域的读、写操作时序都可以单独配置,且每个区域都有片选信号,当片选信号被置低(置0),那么当前用户将访问相应的存储空间(读、写操作)。在本系统中,选用Zone0空间,Zone0占用的外部总线地址为0x2000~0x3FFF,当XA[13]为高电平,XA[14]为低电平时选择ZoneO空间,Zone0片选使能逻辑如图3所示。

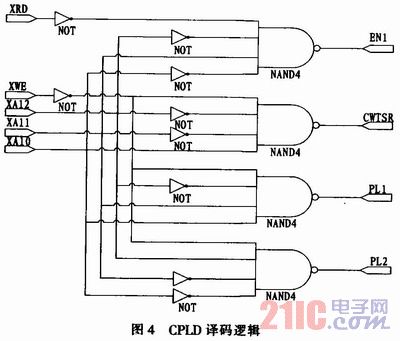

CPLD集成了系统地址选择模块,实现对外部器件的访问。CPLD的逻辑功能决定了HS-3282的功能地址,通过地址译码产生HS-3282所需要的控制信号PL1、PL2、EN1和CWSTR所需要的控制信号。系统中译码模块的逻辑如图4所示。由片选使能和CPLD译码逻辑可得PL1、PL2、EN1和CWSTR的选通地址。

3 系统软件设计

此系统的软件部分主要包括初始化模块、数据的发送/接收子程序模块。

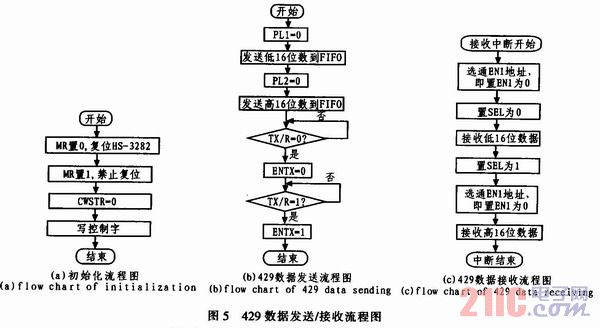

1)初始化模块系统上电后,首先进行初始化,初始化模块包括上电芯片复位和写控制字到HS-3282控制字寄存器。该控制字主要有字长、接收速率、发送速率、源目的解码和自测试设置。初始化流程图如图5(a)所示。

2)ARINC429数据发送模块数据发送是首先向FIFO写入数据,然后经HS-3182驱动发送到总线。在向FIFO写操作过程中,PL1先于PL2有效,多次的写PL1将会使先前的数据被覆盖,PL1有效时,低16位数据被发送到FIFO中。当PL2有效时,高16位数据被传送到FIFO中。第1个数据字写入后TX/R由高变低,然后通过置发送使能信号ENTX,HS-3282将数据字串行发送出去,并自动在相邻两个字之间插入4bit间隔。当FIFO为空时,TX/R由低变高,此时应当禁止发送使能信号ENTX,以便向FIFO重新写入数据。当HS-3282处于发送状态时,不能向FIFO写入数据。发送模块流程图如图5(b)所示。

3)ARINC429数据接收模块 数据接收模块被设计为中断接收,由HS-3282的D/R1提供中断信号。当D/R1为0时,进入中断,并表明ARIN-C429总线上有数据到来,此时选通EN1地址,再置SEL为0,接收低16位数据;接着置SEL为1,再选通EN1地址,接收高16位数据。接收模块流程图如图5(c)所示。

4 结束语

针对ARINC429总线的应用,提出了TMS320F2812与ARINC429总线通信的软硬件设计和实现方案。该设计硬件电路简单,数据通信程序可读性好,编写容易,数据传输准确可靠。在设计TMS320F2812数据总线读写的逻辑控制时,XRD和XWE信号必须参与逻辑控制,保证顺利读写总线数据。经验证该系统能够有效地完成2个16位并行数据到32位串行数据的转换,实现了TMS320F2812 DSP与ARINC429总线之间的数据通信,且传输速率为100 kb,达到了系统的设计要求。该系统可广泛借鉴并应用于ARINC429总线数据传输系统及ARINC429接口卡设计中。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- p 型半导体中电子自旋的“舞蹈”2024/5/28 16:10:43

- BiCMOS 运算放大器的知识2024/4/16 17:41:17

- 模数转换 – 性能标准2024/4/8 16:37:02

- 解析 PWM (DAC) 性能:第 4 部分 – 非均匀占空比组2024/3/28 17:23:37

- 了解运算放大器的输出信号摆幅2024/3/18 16:29:20