浅谈低功耗概述及特性优势

出处:木头东瓜 发布于:2011-09-01 22:58:22

概述

由于功耗敏感应用大幅增加,加上功率预算日益紧张,低的系统功耗已成为越来越多应用的需要。当今,FPGA技术更多地用于低功耗设备,这使得降低系统功耗成为日益重要的挑战。近年来,FPGA因为采用了能降低成本的先进的工艺技术,应用也日益广泛。但在成本降低的同时,功耗也因为高的晶体管漏电流而增加。不同的FPGA技术有显著不同的功耗方式,这些差异对系统整体设计和功率预算有着深远的影响。Actel的超低功耗flash FPGA功耗,提供精选功率模式,且封装尺寸小,在业界居于地位。

特性和优势

总系统功耗

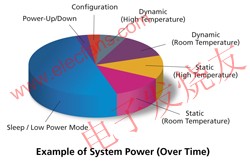

在评估不同FPGA技术的功耗时,需要考虑以下五种基本功耗元素:

静态功耗

动态功耗

上电功耗 (或起动功耗)

配置功耗

睡眠模式 (或低功耗模式) 功耗

这些减少了一个终端系统的总功耗,而这反过来又有望降低我们对于化石燃料的依赖。由于可以将较低的功耗直接视为等同于所需电力的减少,因此使得上述目标得以实现。而且,较少的电力消耗首先意味着产生电能所需的化石燃料的减少。相应地,这将有助于减少对于我们所居住星球的大气和气候具有负面影响的温室气体。 总体系统功耗是五种功耗元素按时间比例的组合。

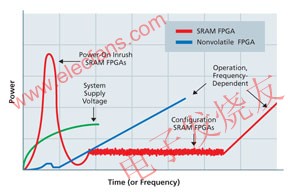

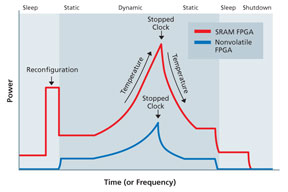

下面的对比图表给出了基于SRAM的FPGA与基于 flash/反熔丝技术的非易失性FPGA的功耗比较,其中,左边为上电功耗方式,右边为不同运作模式的功耗。

功率方式与功耗

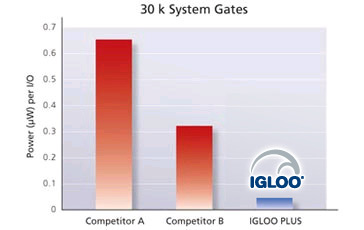

相比接近的低功耗竞争产品,采用Actel IGLOO器件能够延长电池寿命达10倍,若采用Actel 的IGLOO PLUS器件,每I/O的功耗更低至接近低功耗竞争产品的16分之一。这是因为Actel的产品在系统运行的所有五个阶段中具有出色的总体功率方式及更低的功耗。功耗一般分两种:来自开关的动态功耗,和来自漏电的静态功耗。而动态功耗又可分为电容充放电(包括网络电容和输入负载),还有当P/N MOS 同时打开形成的瞬间短路电流。静态功耗也可分为几类:扩散区和衬底形成二极管的反偏电流(Idiode),另外一类是关断晶体管中通过栅氧的电流(Isubthreshold)。芯片的漏电会随温度变化,所以当芯片发热时,静态功耗指数上升。另外漏电流也会随特征尺寸减少而增加。

下图所示为每款器件的电池寿命和每I/O功耗的比较,有关数据是基于厂商的软件功率分析工具。

下一篇:浅谈CRC标准及计算过程

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 深入解析嵌入式 OPENAMP 框架:开启异核通信新时代2025/7/22 16:27:29

- 一文快速了解OPENWRT基础知识2025/7/14 16:59:04

- 独立 ADC 优势大揭秘:为何不可替代?2025/7/7 16:21:04

- 深入剖析:嵌入式中 RS485、RS422 和 RS232 的特点差异2025/7/5 15:07:54

- 揭秘嵌入式 MCU:浮点数据处理难点及应对策略2025/6/20 15:19:07