如何通过电源去耦来保持电源进入集成电路(IC)的各点的低阻抗?

出处:电子产品世界 发布于:2018-11-08 14:00:29

如何通过电源去耦来保持电源进入集成电路(IC)的各点的低阻抗?

诸如放大器和转换器等模拟集成电路具有至少两个或两个以上电源引脚。对于单电源器件,其中一个引脚通常连接到地。如ADC和DAC等混合信号器件可以具有模拟和数字电源电压以及I/O电压。像FPGA这样的数字IC还可以具有多个电源电压,例如内核电压、存储器电压和I/O电压。

不管电源引脚的数量如何,IC数据手册都详细说明了每路电源的允许范围,包括推荐工作范围和,而且为了保持正常工作和防止损坏,必须遵守这些限制。

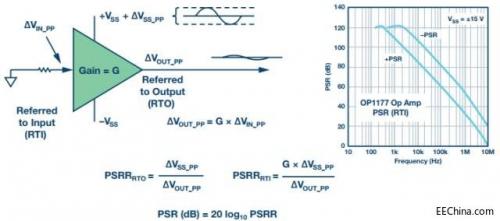

然而,由于噪声或电源纹波导致的电源电压的微小变化—即便仍在推荐的工作范围内—也会导致器件性能下降。例如在放大器中,微小的电源变化会产生输入和输出电压的微小变化,如图1所示。

图1. 放大器的电源抑制显示输出电压对电源轨变化的灵敏度。

放大器对电源电压变化的灵敏度通常用电源抑制比(PSRR)来量化,其定义为电源电压变化与输出电压变化的比值。

图1显示了典型高性能放大器(OP1177)的PSR随频率以大约6dB/8倍频程(20dB/10倍频程)下降的情况。图中显示了采用正负电源两种情况下的曲线图。尽管PSRR在直流下是120dB,但较高频率下会迅速降低,此时电源线路上有越来越多的无用能量会直接耦合至输出。

如果放大器正在驱动负载,并且在电源轨上存在无用阻抗,则负载电流会调制电源轨,从而增加交流信号中的噪声和失真。

尽管数据手册中可能没有给出实际的PSRR,数据转换器和其他混合信号IC的性能也会随着电源上的噪声而降低。电源噪声也会以多种方式影响数字电路,包括降低逻辑电平噪声容限,由于时钟抖动而产生时序错误。

上一篇:技术文章:巧用电源模块

下一篇:简单的LM317可调电源

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 双向全桥 DC - DC 变换器助力船舶应急电源高效运行2026/4/28 16:32:29

- LDO 与线性电源的差异及 LDO 特性2026/4/28 15:50:39

- MOS 管在开关电源及马达驱动中的全面解析2026/4/24 14:00:32

- 揭秘开关电源与变压器:优缺点大比拼2026/4/23 15:36:08

- 掌握这些措施,降低开关电源纹波和噪声电压2026/4/23 15:04:22