Achronix - 实测!AlexNet卷积核在FPGA占90%资源仍跑750MHz|算力达288万张图像/秒

出处:厂家供稿 发布于:2020-06-15 17:15:19

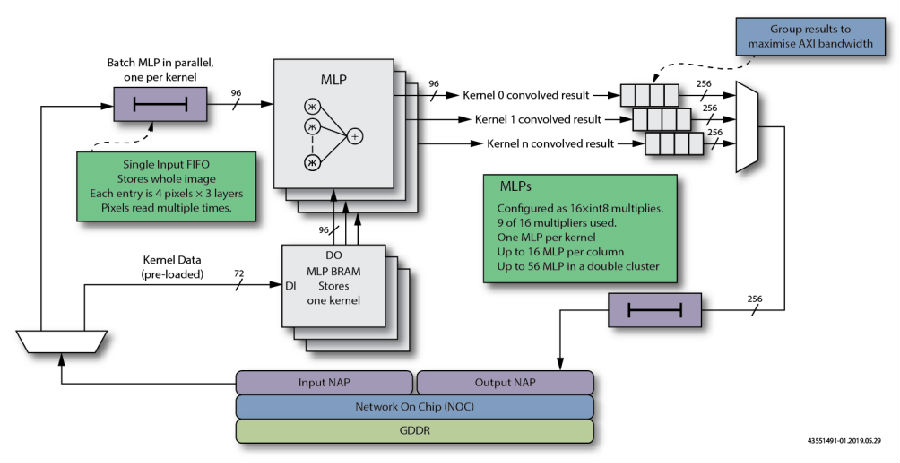

MLP_Conv2D是功能齐全的设计,可将2D输入图像与多个内核同时进行卷积。 该设计充分利用了MLP和BRAM模块,每个MLP一个周期执行12个int8乘法。此外,MLP列和BRAM块均等级联以有效地将图像数据传递,从而允许同时处理多个内核。

该设计使用NoC接入点(NAP)从片上网络(NoC)读取或写入数据。NoC连接到SpeedSTer7t器件中的GDDR6控制器再到外部存储器。

AlexNet

尽管初为AlexNet图像和内核大小配置了MLP_Conv2D设计,但是2D卷积是一个通用过程,因此可以重新配置该设计并使其适应许多不同的2D方法。

2D卷积的一般原理是在图像(实际上是另一个2D矩阵)上传递内核(2D矩阵)。对于每次计算,内核均以输入图像的像素为中心,并对每个内核值(称为权重)与其当前对齐的像素执行乘法运算。这些乘法的总和给出了原始图像像素的特定卷积结果。然后将内核移至下一个像素,并重复该过程。

经过训练的内核,2D卷积生成一个输出结果图像,突出显示输入图像的特定特征,例如垂直线,水平线,变化角度的对角线和变化半径的曲线。然后可以将这些特征输入到其他处理层(包括其他2D卷积),然后可以将其标识为(通常在软件中)为特定对象。

因此,二维卷积处理不应被视为图像识别的完整解决方案,而应被视为处理操作链中的单个关键组件。

乘法密度

2D卷积的挑战是所需的乘法数量,这就是MLP中专用的乘法器阵列。对于AlexNet配置,每个内核为11×11= 121个权重值。但是,卷积实际上是3D的,因为输入图像具有三层(RGB),因此一组内核有121×3 = 363个乘法来产生单个输出结果。AlexNet输入图像为227×227;但是,此图像的stride为4(在计算之间内核移动了四个像素)。此过程导致输出结果矩阵为54×54 = 2916个结果。因此,对于一幅图像需要363×2916 = 1,058,508次乘法;即处理一个图像需要进行一百万次以上的累加运算。其中单个Kernel进行2D卷积的动态示意图如下:

图表 1 单个Kernel进行2D卷积的动态示意图

对于MLP_Conv2D,其设计旨在处理一幅图像中的60个内核,单次执行超过6000万次乘法累加操作。

性能

MLP_Conv2D设计可以以750 MHz的频率运行。单个MLP能够在137 ?s内对具有11×11内核的单个227×227 RGB输入图像进行卷积,相当于每秒15.4GOPS(包含乘和加)。 但一个MLP_Conv2D实例由60个并行运行的MLP构成,可以同时对60个输入图像进行卷积,相当于924GOPS。 ,将多达40个MLP_Conv2D实例化到单个器件中,每个实例都通过自己的NAP将数据传输到GDDR6存储器,从而实现了组合高达37 TOPS的性能-相当于每秒处理28,8000张图像(本设计主要针对卷积核)。

资源

MLP_Conv2D围绕MLP和BRAM块功能而设计,并使用它们各自的内部级联走线。 同样,NAP允许直接从外部存储器路由数据互联。这些功能可实现的附加逻辑或路由要求,利用率表如下:

图表 2 单个MLP_Conv2D实例资源使用

图表 3 并行40个MLP_Conv2D实例资源使用

图表 4 MLP_Conv2D框图

数据流:单个MLP

每个MLP都有一个邻近的BRAM。 在此设计中BRAM用于存储内核并将其多次传递到MLP。 初始化时,将从输入NAP中读取不同的内核,并将其写入相应的BRAM。 BRAM在写侧配置为72位,而读取设置为144位。在操作期间,仅将96位用作内核权重,即读取为4个权重×3层×8位。初始图像数据从NAP读取到输入FIFO中,该输入FIFO用于将图像存储为一系列行。尽管此输入存储器被列为FIFO,但仍可作为可重复读取的FIFO,因为可以多次从中读取行。该存储器配置为144位宽,仅使用96位,由两个BRAM72K组成。每个字由4个像素×3层×8位组成。初始化时,将读取足够的行以匹配内核中的行数加上垂直跨步所需的行数。即

一旦加载了初始数据和内核,便开始计算。

从输入FIFO中读取条图像行,并读取与内核水平大小匹配的图像数据像素数量。在读取这些像素时,将读取匹配的内核权重。MLP将这些96位流的每一个乘以12个int8值并累加结果。输入FIFO前进到第二行,重复此过程,直到内核的所有行都与输入图像左上角的适当像素相乘。在此过程中,MLP积累了结果;现在,该结果是图像与内核卷积的左上角的2D卷积。该结果以16位结果的形式从MLP输出。重复此过程,输入FIFO跨行超前STRIDE参数设置的像素数(对于当前设计,STRIDE固定为4)。在每个处理周期包括在内时,都会生成另一个结果,直到水平地获取了适当数量的结果为止。

然后,将输入FIFO下移STRIDE行数,然后重复该过程以生成输入图像中下一组线的卷积结果。当输入FIFO向下移动时,不再需要FIFO中的初始行,因此与MLP计算并行时,将加载下一组用于输入图像的STRIDE行。考虑外部存储源的带宽要求时,可以看到映像和内核仅从内存中读取。然后,它们可以从各自的BRAM中重新使用,从而减少了外部存储器带宽的总体负担,其过程参考图表1。

数据流:多个MLP

MLP的一个显著特点是能够将数据和结果从一个MLP或BRAM级联到同一列中。 MLP_Conv2D通过将MLP及其关联的BRAM放在列组中来利用这些级联路径。在将BRAM加载到内核时,级联路径用于将数据流水线传输到每个BRAM,并且使用BRAM块地址模式选择要写入内核的BRAM。

在计算过程中,输入的图像数据将在MLP的列中级联,以便每个MLP在其下一个邻居之后的一个周期接收到图像数据。同时,控制内核读取的BRAM读取地址以一个周期的延迟级联到BRAM列中。这样,每个MLP在其先前的MLP之后一个周期接收相同的图像数据和相同的内核读取地址。每个MLP的计算差异在于,其关联的BRAM将具有不同的内核数据。结果是一个图像并行地与多个内核卷积。并行卷积的数量称为BATCH。

数据流:计算结果

如前所述,每个MLP为内核和图像部分的每个卷积生成16位结果。

MLP排列在16列中,因此从该列中生成一个256位字,该字由该列中每个MLP的结果组成。然后将此256位字写入输出NAP。 这种安排导致卷积结果作为同一图像的图层存储在内存中;因此,当三层或RGB存储在单个输入字中时,匹配输入字排列。

然后,由于可以在完整的256位结果上的16个并行实例中执行激活功能,因此该安排允许将涉及的结果并行处理到激活层中。同样,一旦256位结果通过输出NAP写回到存储器中,则可以将结果读回到另一个2D卷积电路中。

图表 5 MLP_Conv2D布局示意图

布局

在Speedster7t架构中,每个NAP对应32个MLP。该设计经过优化,可使用两个NAP,一个用于读取,一个用于写入,因此可以对应64个MLP。

但是,输入和输出FIFO需要两个BRAM 72K存储块才能创建一个256位宽的组合存储器。因此,这些存储器将消耗64个可用位置中的四个用于数据I / O。

设计被安排为使用与两个NAP相关联的四列MLP。但是,列和一列都使用14个MLP,剩下两个MLP位置分别用于输入和输出FIFO。中间两列使用所有16??个可用的MLP。在平面图中,各列的排列方式是使列(底部具有输入FIFO存储器)与NAP相邻,以改善时序。

下面显示了一个实例,即使用了60个MLP(Batch=60)的设计实际布局图(突出显示了路线):

图表 6 60个MLP布局图

在全芯片构建中使用40个实例时,尽力使每个实例都使用NAP与内存进行通信。结果,FMax仍能达到750MHz,并使用掉芯片中的所有80个NAP以及94%的MLP和BRAM72K。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 哈夫曼编码原理详解及应用实例2024/5/7 17:46:36

- 人工智能(AI)的发展带来了许多利与弊:2024/5/7 17:34:35

- 常见的激光雷达slam算法有哪些?2024/4/30 17:24:16

- 什么叫特高压电网2024/4/30 17:21:31

- 分布式光伏发电有什么优劣势2024/4/29 17:17:39